网络时钟发生器,两路输出 Network Clock Generator, Two Outputs

Product Details

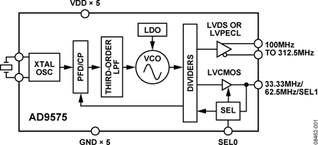

The AD9575 provides a highly integrated, dual output clock generator function including an on-chip PLL core that is optimized for network clocking. The integer-N PLL design is based on the Analog Devices, Inc., proven portfolio of high performance, low jitter frequency synthesizers to maximize line card performance. Other applications with demanding phase noise and jitter requirements also benefit from this part.

The PLL section consists of a low noise phase frequency detector PFD, a precision charge pump, a low phase noise voltage controlled oscillator VCO, and pin selectable feedback and output dividers. By connecting an external crystal, popular network output frequencies can be locked to the input reference. The output divider and feedback divider ratios are pin programmable for the required output rates. No external loop filter components are required, thus conserving valuable design time and board space.

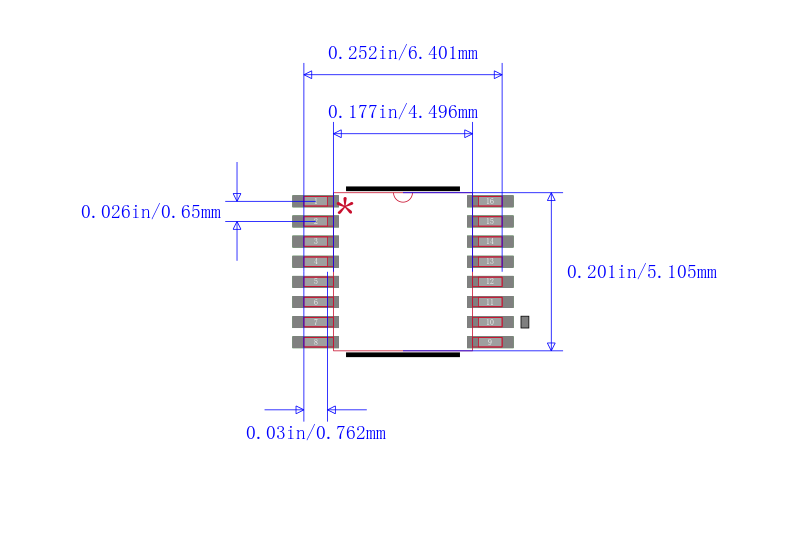

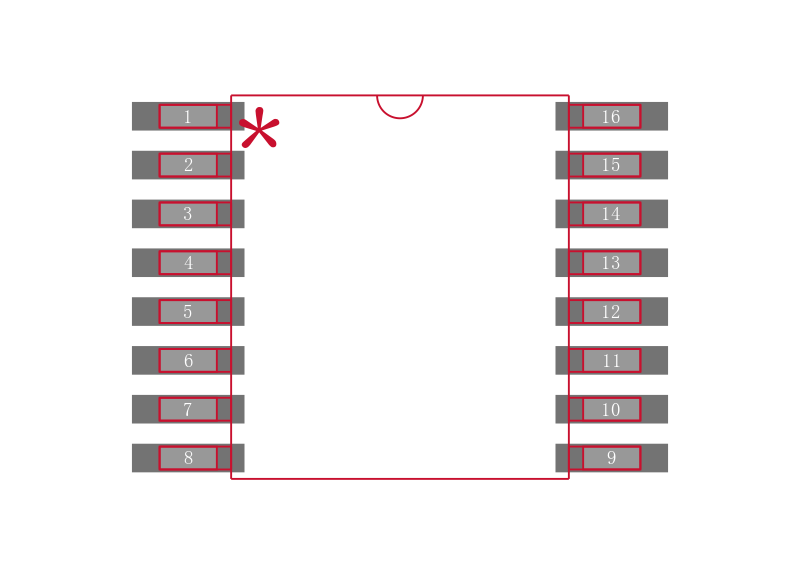

The AD9575 is available in a 16-lead, 4.4 mm × 5.0 mm TSSOP and can be operated from a single 3.3 V supply. The temperature range is −40°C to +85°C.

** Applications**

- .

- GbE/FC/SONET line cards, switches, and routers

- .

- CPU/PCI-E applications

- .

- Low jitter, low phase noise clock generation

### Features and Benefits

- .

- Fully integrated VCO/PLL core

- .

- 0.39 ps rms jitter from 12 kHz to 20 MHz at 156.25 MHz

- .

- 0.15 ps rms jitter from 1.875 MHz to 20 MHz at 156.25 MHz

- .

- 0.40 ps rms jitter from 12 kHz to 20 MHz at 106.25 MHz

- .

- 0.15 ps rms jitter from 637 kHz to 10 MHz at 106.25 MHz

- .

- Input crystal frequency of 19.44 MHz, 25 MHz, or 25.78125 MHz

- .

- Pin selectable divide ratios for 33.33 MHz, 62.5 MHz,

100 MHz, 106.25 MHz, 125 MHz, 155.52 MHz, 156.25 MHz,

159.375 MHz, 161.13 MHz, and 312.5 MHz outputs

- .

- LVDS/LVPECL/LVCMOS output format

- .

- Integrated loop filter

- .

- Space saving 4.4 mm × 5.0 mm TSSOP

- .

- See data sheet for additional features

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

AD9575ARUZLVD ADI 亚德诺 | 当前型号 | 当前型号 |

AD9575ARUZPEC 亚德诺 | 完全替代 | AD9575ARUZLVD和AD9575ARUZPEC的区别 |