四通道,14位, 80 MSPS / 105 MSPS / 125 MSPS Quad, 14-Bit, 80 MSPS/105 MSPS/125 MSPS

GENERAL DESCRIPTION

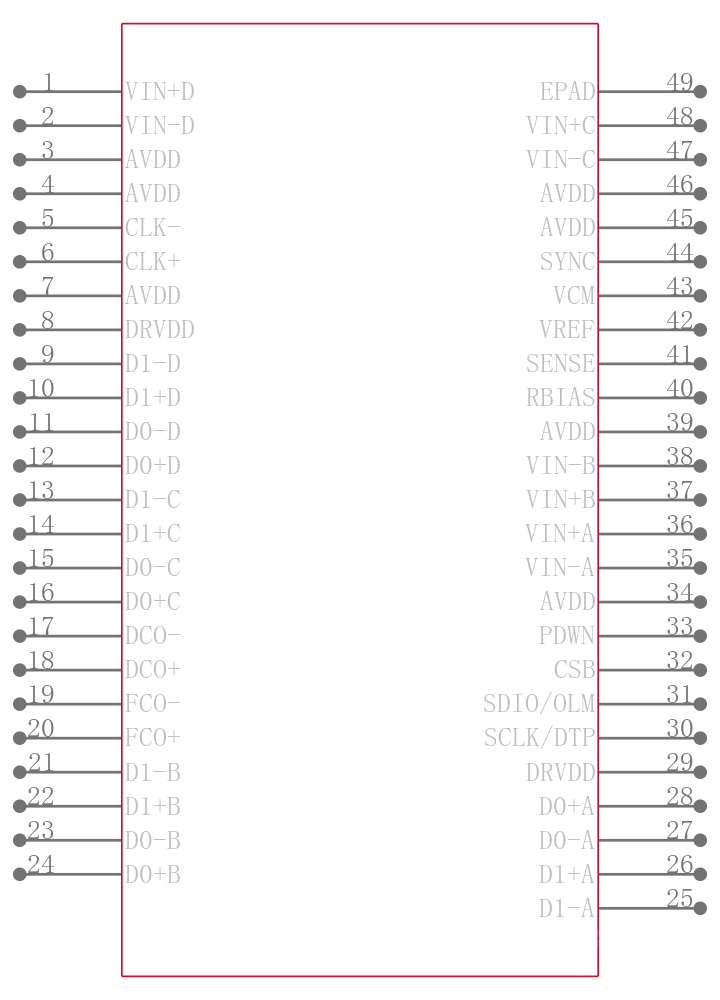

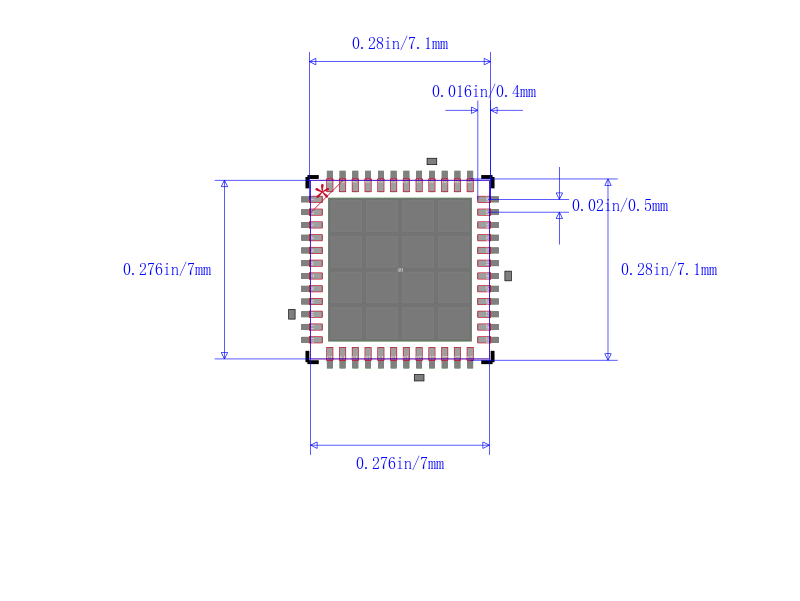

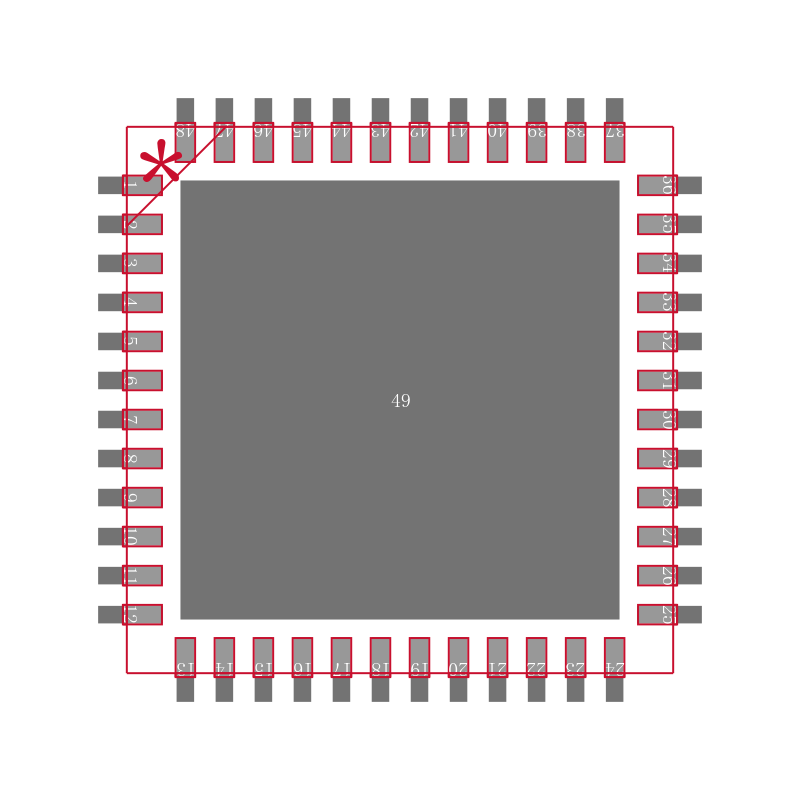

The AD9253 is a quad, 14-bit, 80 MSPS/105 MSPS/125 MSPS analog-to-digital converter ADC with an on-chip sample and-hold circuit designed for low cost, low power, small size, and ease of use. The product operates at a conversion rate of up to 125 MSPS and is optimized for outstanding dynamic performance and low power in applications where a small package size is critical.

The ADC requires a single 1.8 V power supply and LVPECL-/CMOS-/LVDS-compatible sample rate clock for full performance operation. No external reference or driver components are required for many applications.

FEATURES

1.8 V supply operation

Low power: 110 mW per channel at 125 MSPS with scalable power options

SNR = 74 dB to Nyquist

SFDR = 90 dBc to Nyquist

DNL = ±0.75 LSB typical; INL = ±2.0 LSB typical

Serial LVDS ANSI-644, default and low power, reduced signal option similar to IEEE 1596.3

650 MHz full power analog bandwidth

2 V p-p input voltage range

Serial port control

Full chip and individual channel power-down modes

Flexible bit orientation

Built-in and custom digital test pattern generation

Multichip sync and clock divider

Programmable output clock and data alignment

Programmable output resolution

Standby mode

APPLICATIONS

Medical ultrasound

High speed imaging

Quadrature radio receivers

Diversity radio receivers

Test equipment

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

AD9253BCPZRL7-80 ADI 亚德诺 | 当前型号 | 当前型号 |

AD9253BCPZ-80 亚德诺 | 完全替代 | AD9253BCPZRL7-80和AD9253BCPZ-80的区别 |

AD9253BCPZ-125 亚德诺 | 类似代替 | AD9253BCPZRL7-80和AD9253BCPZ-125的区别 |

AD9253BCPZ-105 亚德诺 | 类似代替 | AD9253BCPZRL7-80和AD9253BCPZ-105的区别 |