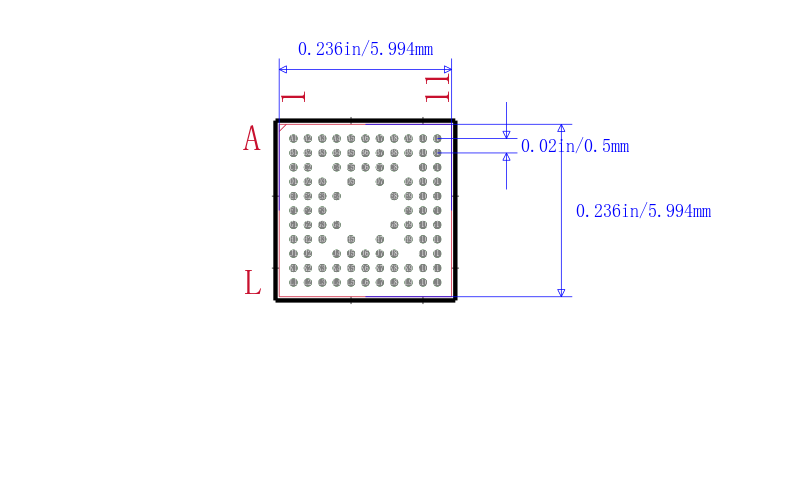

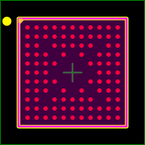

CPLD MAX II Family 440 Macro Cells 201.1MHz 0.18um Technology 2.5V/3.3V 100Pin Micro FBGA

* Low-cost, low-power CPLD * Instant-on, non Volatile architecture * Standby current as low as 25 µA * Provides fast propagation delay and clock-to-output times * Provides four global clocks with two clocks available per logic array block LAB * UFM block up to 8 Kbits for non Volatile storage * MultiVolt core enabling external supply voltages to the device of either 3.3 V/2.5 V or 1.8 V * MultiVolt I/O interface supporting 3.3 V, 2.5 V, 1.8 V, and 1.5 V logic levels * Bus-friendly architecture including programmable slew rate, drive strength, bus-hold, and programmable pull-up resistors * Schmitt triggers enabling noise tolerant inputs programmable per pin * I/Os are fully compliant with the Peripheral Component Interconnect Special Interest Group PCI SIG PCI Local Bus Specification, Revision 2.2 for 3.3 V operation at 66 MHz * Supports hot-socketing * Built-in Joint Test Action Group JTAG boundary-scan test BST circuitry compliant with IEEE Std. 1149.1-1990 * ISP circuitry compliant with IEEE Std. 1532