ON SEMICONDUCTOR MC100EP210SFAG CLOCK DRIVER, DUAL, 1GHZ, LQFP-32 新

The MC100EP210S is a low skew 1-to-5 dual differential driver, designed with LVDS clock distribution in mind. The LVDS or LVPECL input signals are differential and the signal is fanned out to five identical differential LVDS outputs. The EP210S specifically guarantees low output-to-output skew. Optimal design, layout, and processing minimize skew within a device and from device to device. Two internal 50-ohm resistors are provided across the inputs. For LVDS inputs, VTA and VTB pins should be unconnected. For LVPECL inputs, VTA and VTB pins should be connected to the V Designers can take advantage of the EP210S performance to distribute low skew LVDS clocks across the backplane or the board. Special considerations are required for differential inputs under No Signal conditions to prevent instability.

Features

---

|

- .

- 20 ps Typical Output-to-Output Skew

- .

- 85 ps Typical Device-to-Device Skew

- .

- 550 ps Typical Propagation Delay

- .

- The 100 Series contains temperature compensation.

- .

- Maximum Frequency > 1 Ghz

- .

- Operating Range: VCC = 2.375 V to 2.625 V with VEE = 0 V

- .

- Internal 50Ω Input Termination Resistors

- .

- LVDS Input/Output Compatible

- .

- Pb-Free Packages are Available

频率 1 GHz

电源电压DC 2.50 V

无卤素状态 Halogen Free

输出接口数 5

供电电流 150 mA

电路数 2

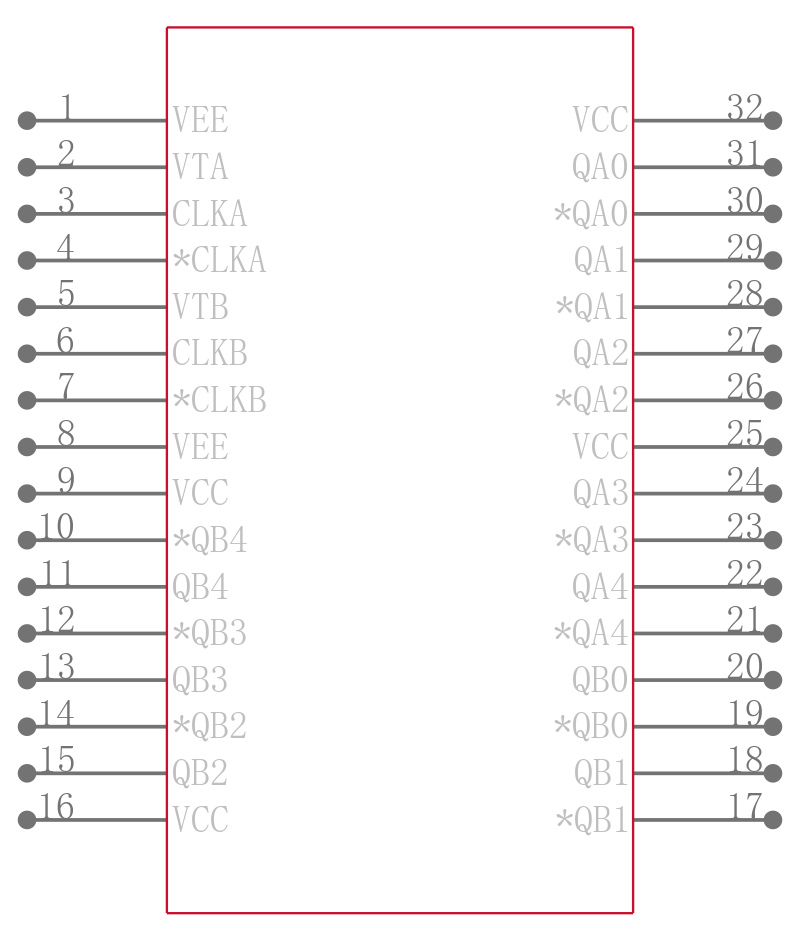

针脚数 32

工作温度Max 85 ℃

工作温度Min -40 ℃

电源电压 2.375V ~ 2.625V

电源电压Max 2.625 V

电源电压Min 2.375 V

安装方式 Surface Mount

引脚数 32

封装 LQFP-32

长度 7 mm

宽度 7 mm

高度 1.45 mm

封装 LQFP-32

工作温度 -40℃ ~ 85℃

产品生命周期 Active

包装方式 Tray

制造应用 High Performance Logic for test systems and work stations. Clock fan out in routers, switches and other networking applications

RoHS标准 RoHS Compliant

含铅标准 Lead Free

REACH SVHC版本 2015/12/17

ECCN代码 EAR99

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

MC100EP210SFAG ON Semiconductor 安森美 | 当前型号 | 当前型号 |

MC100EP210SFATWG 安森美 | 完全替代 | MC100EP210SFAG和MC100EP210SFATWG的区别 |

MC100LVEP111FAG 安森美 | 类似代替 | MC100EP210SFAG和MC100LVEP111FAG的区别 |

MC100LVEP111FARG 安森美 | 类似代替 | MC100EP210SFAG和MC100LVEP111FARG的区别 |