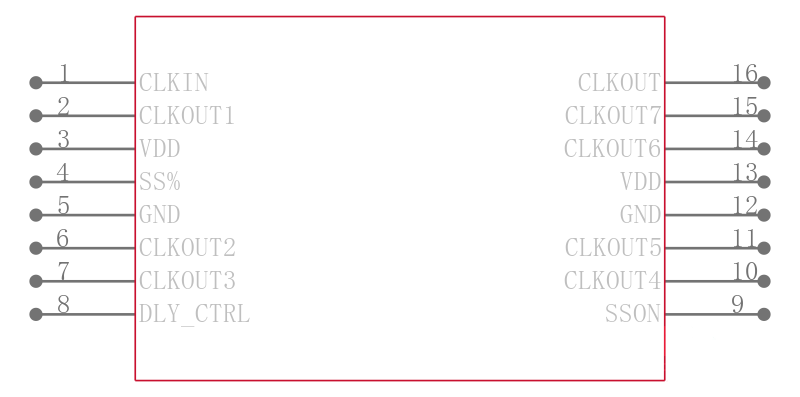

P3P623S00EG-16TR概述

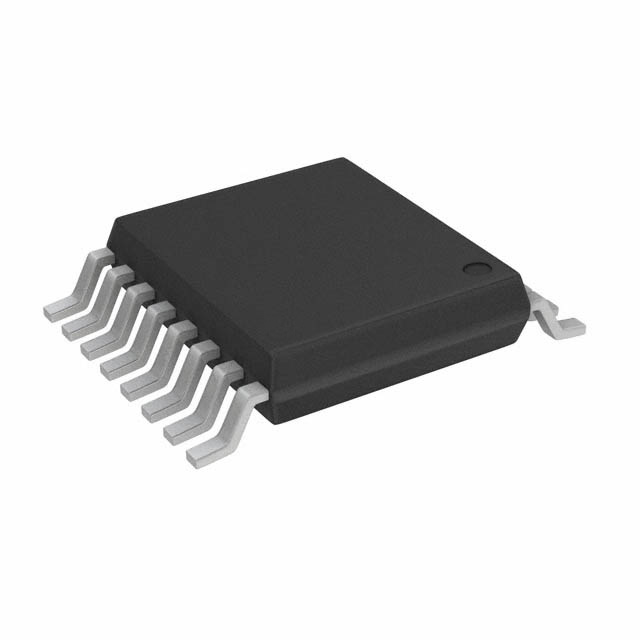

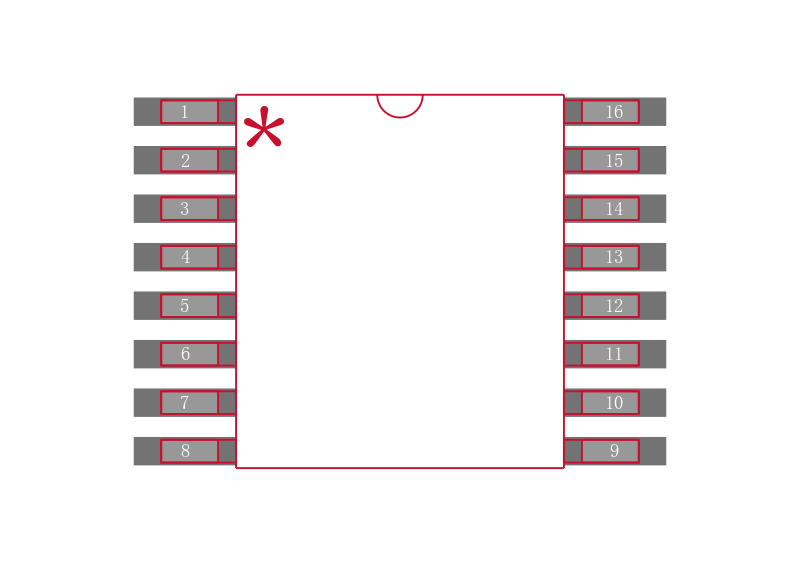

Zero Delay PLL Clock Buffer Single 16Pin TSSOP T/R

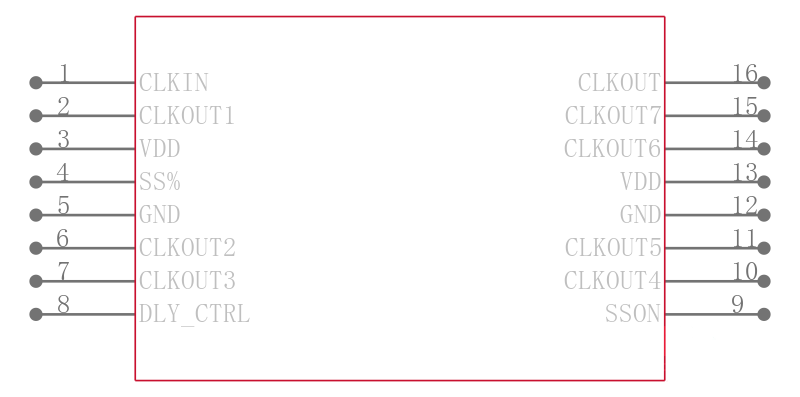

P3P623S00B/E is a versatile, 3.3V zero-dealy buffer designed to distribute Timing-Safe™ clocks with peak EMI reduction.P3P623S00B is an eight pin version, accepts one reference input and drives out one low skew Timing-Safe™ clock.P3P623S00E accepts one reference input and drives out eight low-skew Timing-Safe™clocks.P3P623S0B/E has an SS% that selects two different deviation and associated Input-Output skewTskew.P3P623S00E has a CLKOUT for adjusting the Input-Output clock dealy, depending upon the value of capacitor connected at this pin to GND.P3P623S00B/E operates from a 3.3V supply and is available in two different packages, as shown in the ordering information table.

Features

---

|

- .

- Clock distribution with Timing-Safe Peak EMI Reduction

- .

- 2 different Spread Selection options

- .

- Spread Spectrum can be turned ON/OFF

P3P623S00EG-16TR中文资料参数规格

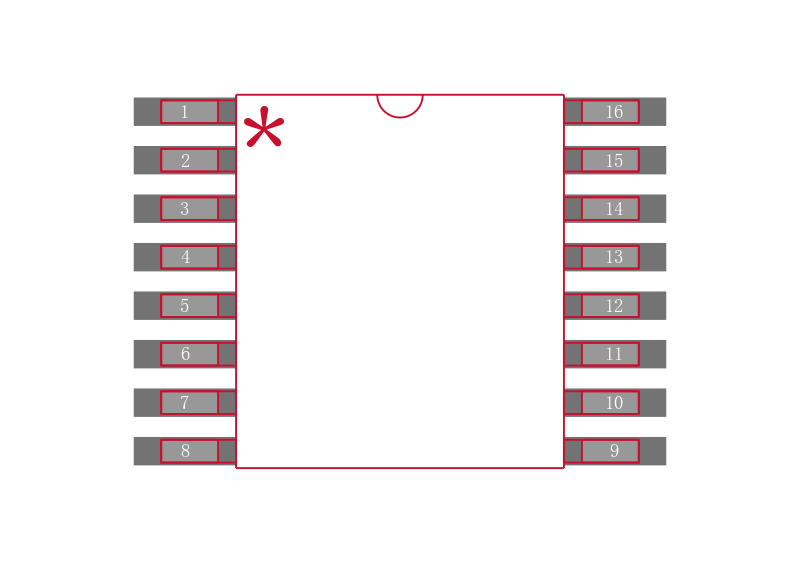

P3P623S00EG-16TR引脚图与封装图

在线购买P3P623S00EG-16TR

型号: P3P623S00EG-16TR

制造商:

ON Semiconductor

安森美

描述:Zero Delay PLL Clock Buffer Single 16Pin TSSOP T/R