PIC18F46K20-E/MV概述

28 /40/ 44引脚闪存单片机采用纳瓦XLP技术 28/40/44-Pin Flash Microcontrollers with nanoWatt XLP Technology

High-Performance RISC CPU:

• C Compiler Optimized Architecture:

\- Optional extended instruction set designed to optimize re-entrant code

• Up to 1024 bytes Data EEPROM

• Up to 64 Kbytes Linear Program Memory Addressing

• Up to 3936 bytes Linear Data Memory Addressing

• Up to 16 MIPS Operation

• 16-bit Wide Instructions, 8-bit Wide Data Path

• Priority Levels for Interrupts

• 31-Level, Software Accessible Hardware Stack

• 8 x 8 Single-Cycle Hardware Multiplier

PIC18F46K20-E/MV中文资料参数规格

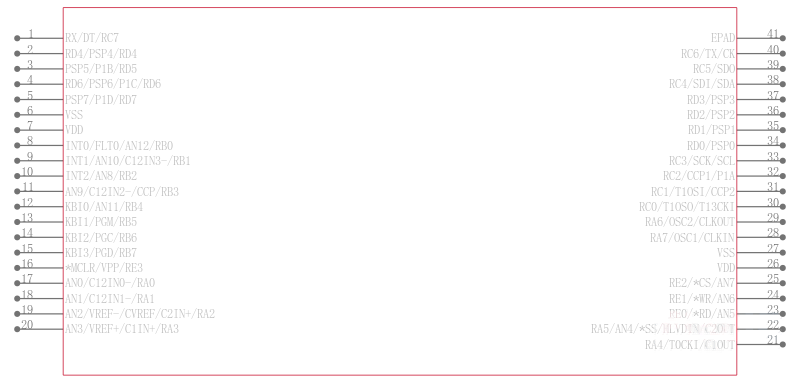

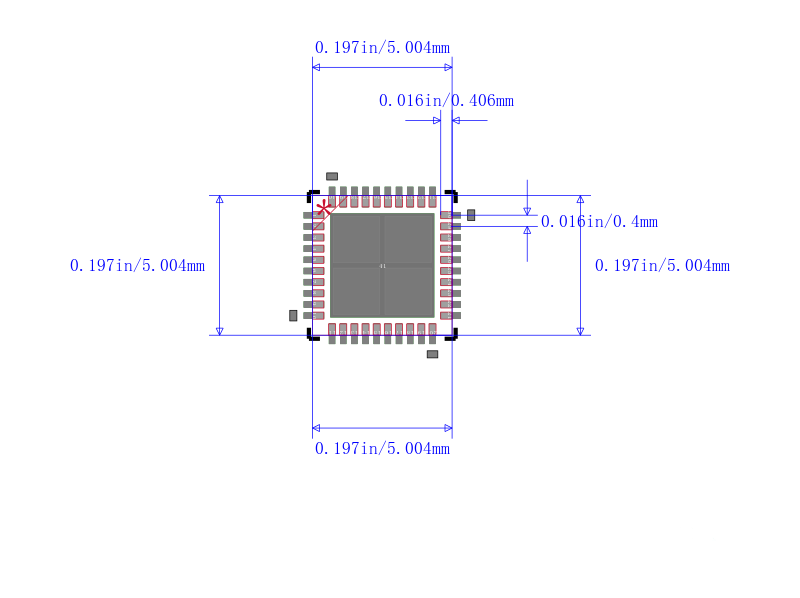

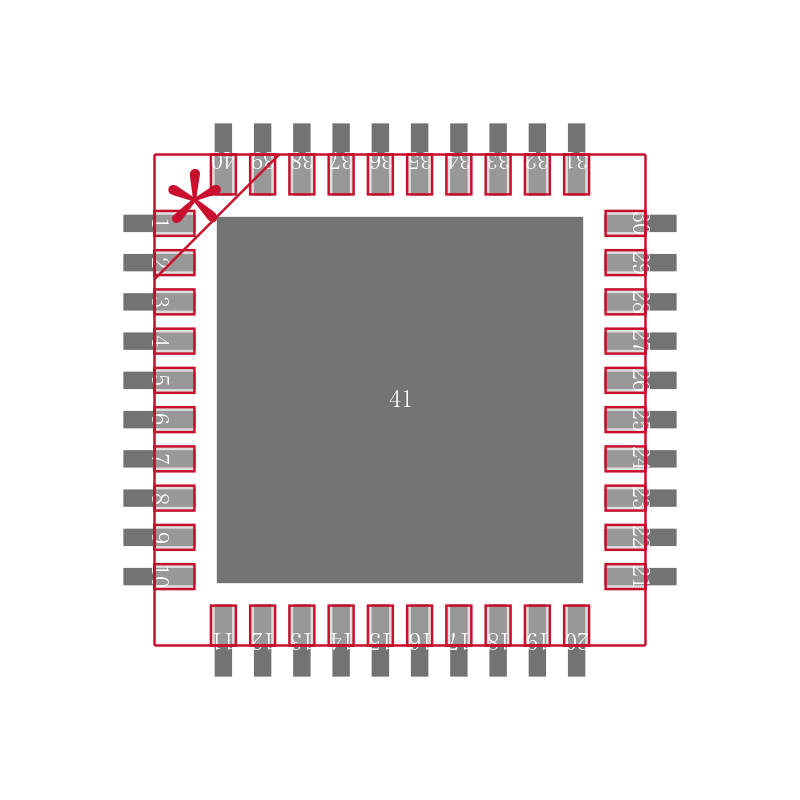

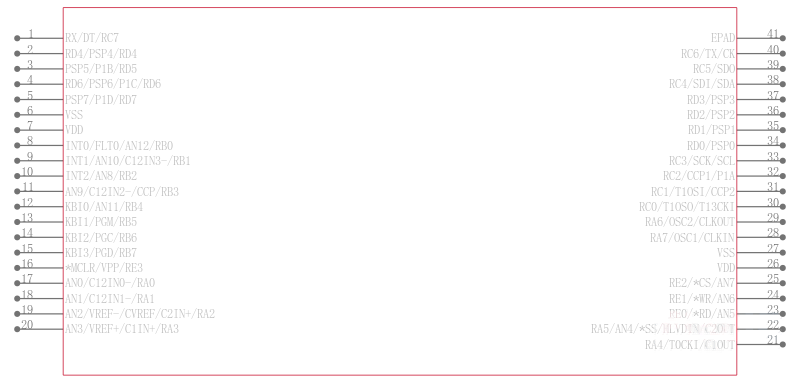

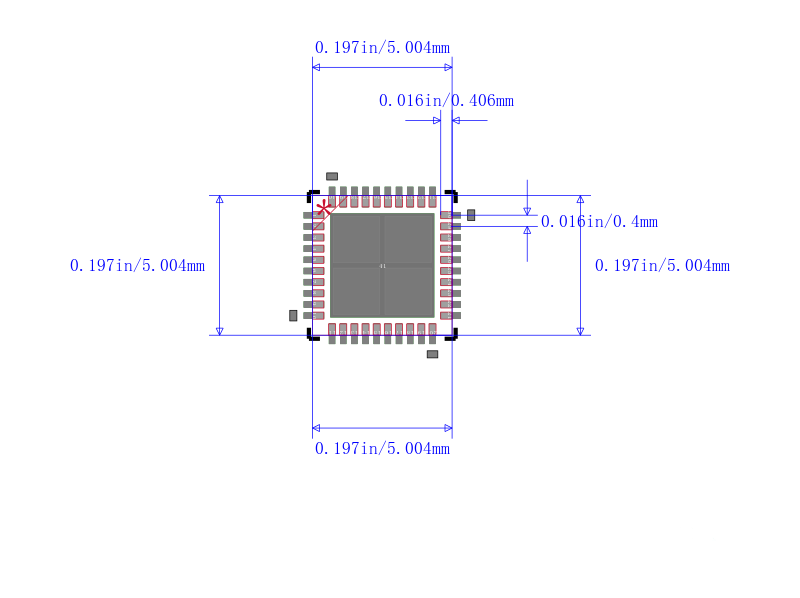

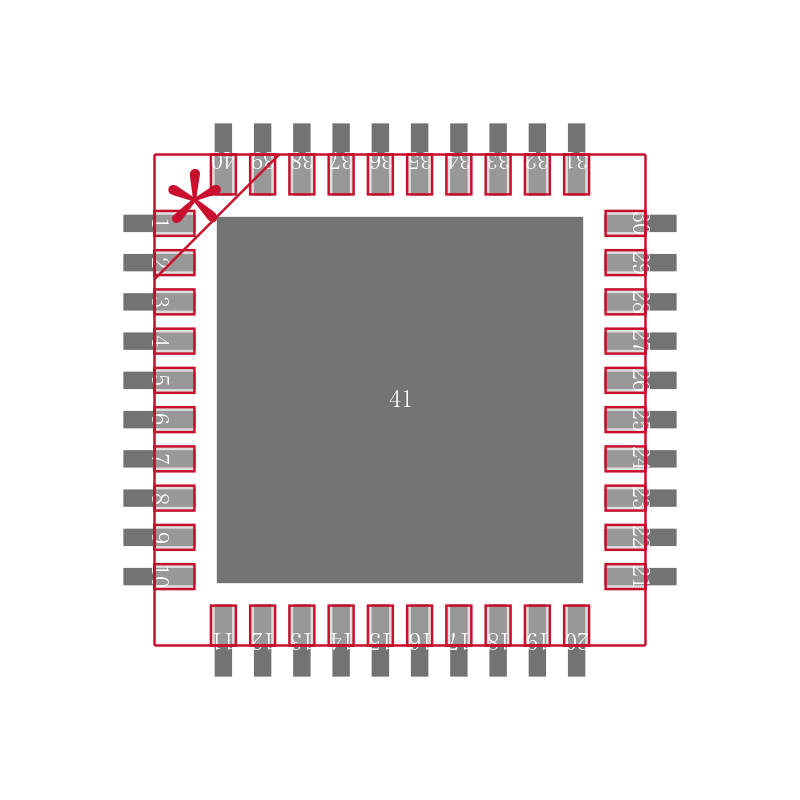

PIC18F46K20-E/MV引脚图与封装图

在线购买PIC18F46K20-E/MV

型号: PIC18F46K20-E/MV

制造商:

Microchip

微芯

描述:28 /40/ 44引脚闪存单片机采用纳瓦XLP技术 28/40/44-Pin Flash Microcontrollers with nanoWatt XLP Technology