电平转换I2C总线中继器, 2输入, 0.9 V至5.5 V电源, 50 mA输出, HWSON-8

Overview

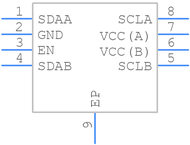

The PCA9517A is a CMOS integrated circuit that provides level shifting between low voltage down to 0.9 V and higher voltage 2.7 V to 5.5 V I²C-bus or SMBus applications. While retaining all the operating modes and features of the I²C-bus system during the level shifts, it also permits extension of the I²C-bus by providing bidirectional buffering for both the data SDA and the clock SCL lines, thus enabling two buses of 400 pF. Using the PCA9517A enables the system designer to isolate two halves of a bus for both voltage and capacitance. The SDA and SCL pins are overvoltage tolerant and are high-impedance when the PCA9517A is unpowered.

The 2.7 V to 5.5 V bus port B drivers behave much like the drivers on the PCA9515A device, while the adjustable voltage bus port A drivers drive more current and eliminate the static offset voltage. This results in a LOW on the port B translating into a nearly 0 V LOW on the port A which accommodates smaller voltage swings of lower voltage logic.

The static offset design of the port B PCA9517A I/O drivers prevent them from being connected to another device that has rise time accelerator including the PCA9510, PCA9511, PCA9512, PCA9513, PCA9514, PCA9515A, PCA9516A, PCA9517A port B, or PCA9518. Port A of two or more PCA9517As can be connected together, however, to allow a star topography with port A on the common bus, and port A can be connected directly to any other buffer with static or dynamic offset voltage. Multiple PCA9517As can be connected in series, port A to port B, with no build-up in offset voltage with only time of flight delays to consider.

The PCA9517A drivers are not enabled unless VCCA is above 0.8 V and VCCB is above 2.5 V. The EN pin can also be used to turn the drivers on and off under system control. Caution should be observed to only change the state of the enable pin when the bus is idle.

The output pull-down on the port B internal buffer LOW is set for approximately 0.5 V, while the input threshold of the internal buffer is set about 70 mV lower 0.43 V. When the port B I/O is driven LOW internally, the LOW is not recognized as a LOW by the input. This prevents a lock-up condition from occurring. The output pull-down on port A drives a hard LOW and the input level is set at 0.3VCCA to accommodate the need for a lower LOW level in systems where the low voltage side supply voltage is as low as 0.9 V.

Table 1. PCA9517 and PCA9517A comparison

Parameter

|

PCA9517[1]

PCA9517A[2]

\---|---|---

electrostatic discharge, HBM

> 2 kV

> 5.5 kV

[1] PCA9517 will be discontinued in several years, so move to the PCA9517A for all new designs and system updates.

[2] The PCA9517A is an improved hot swap and ESD version of the PCA9517, but otherwise operates identically and should be used for all new designs and system updates.

MoreLess

## Features

* 2 channel, bidirectional buffer isolates capacitance and allows 400 pF on either side of the device

* Voltage level translation from 0.9 V to 5.5 V and from 2.7 V to 5.5 V

* Footprint and functional replacement for PCA9515/15A

* I²C-bus and SMBus compatible

* Active HIGH repeater enable input

* Open-drain input/outputs

* Lock-up free operation

* Supports arbitration and clock stretching across the repeater

* Accommodates Standard-mode and Fast-mode I²C-bus devices and multiple masters

* Powered-off high-impedance I²C-bus pins

* Port A operating supply voltage range of 0.9 V to 5.5 V

* Port B operating supply voltage range of 2.7 V to 5.5 V

* 5 V tolerant I²C-bus and enable pins

* 0 Hz to 400 kHz clock frequency the maximum system operating frequency may be less than 400 kHz because of the delays added by the repeater

* ESD protection exceeds 5500 V HBM per JESD22-A114 and 1000 V CDM per JESD22-C101

* Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

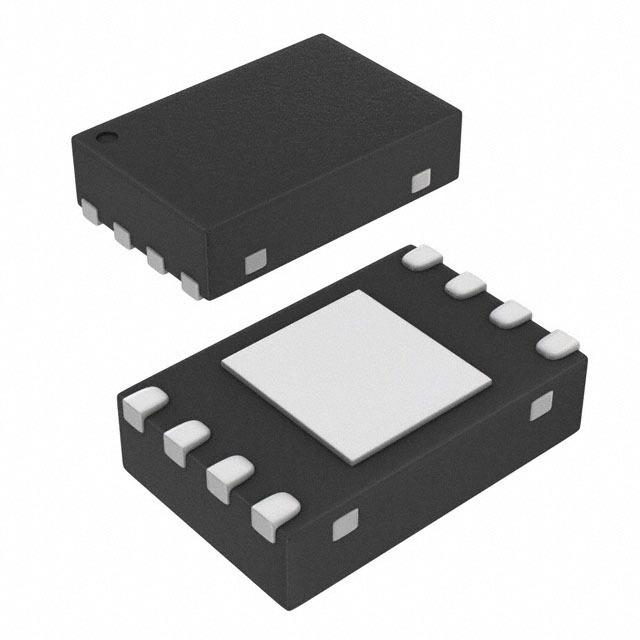

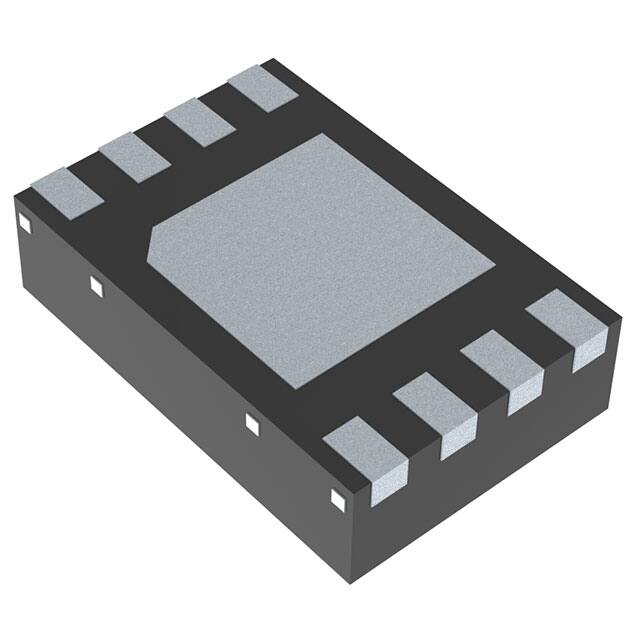

* Packages offered: SO8, TSSOP8 and HWSON8

## Features

输出电流 50 mA

供电电流 5 mA

通道数 2

针脚数 8

耗散功率 100 mW

输入电容 6 pF

输入数 2

工作温度Max 85 ℃

工作温度Min -40 ℃

耗散功率Max 100 mW

电源电压 2.7V ~ 5.5V

电源电压Max 5.5 V

安装方式 Surface Mount

引脚数 8

封装 WFDFN-8

封装 WFDFN-8

工作温度 -40℃ ~ 85℃

产品生命周期 Active

包装方式 Tape & Reel TR

制造应用 I²C

RoHS标准 RoHS Compliant

含铅标准 Lead Free

ECCN代码 EAR99

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

PCA9517ATP,147 NXP 恩智浦 | 当前型号 | 当前型号 |

PCA9517DP,118 恩智浦 | 完全替代 | PCA9517ATP,147和PCA9517DP,118的区别 |

PCA9517D,112 恩智浦 | 完全替代 | PCA9517ATP,147和PCA9517D,112的区别 |

PCA9517D 恩智浦 | 完全替代 | PCA9517ATP,147和PCA9517D的区别 |