高速差动线路接收器 HIGH-SPEED DIFFERENTIAL LINE RECEIVERS

DESCRIPON

The SN55LVDS32, SN65LVDS32, SN65LVDS3486, and SN65LVDS9637 are differential line receivers

that implement the electrical characteristics of low-voltage differential signaling LVDS. This

signaling technique lowers the output voltage levels of 5-V differential standard levels such as

EIA/TIA-422B to reduce the power, increase the switching speeds, and allow operation with a 3.3-V supply rail. Any of the four differential receivers provides a valid logical output state with a ±100-mV differential input voltage within the input common-mode voltage range. The input

common-mode voltage range allows 1 V of ground potential difference between two LVDS nodes.

FEATURES

• Meet or Exceed the Requirements of ANSI TIA/EIA-644 Standard

• Operate With a Single 3.3-V Supply

• Designed for Signaling Rates of up to 100 Mbps See Table 1

• Differential Input Thresholds ±100 mV Max

• Typical Propagation Delay Time of 2.1 ns

• Power Dissipation 60 mW Typical Per Receiver at Maximum Data Rate

• Bus-Terminal ESD Protection Exceeds 8 kV

• Low-Voltage TTL LVTTL Logic Output Levels

• Pin Compatible With AM26LS32, MC3486, and μA9637

• Open-Circuit Fail-Safe

• Cold Sparing for Space and High Reliability Applications Requiring Redundancy

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

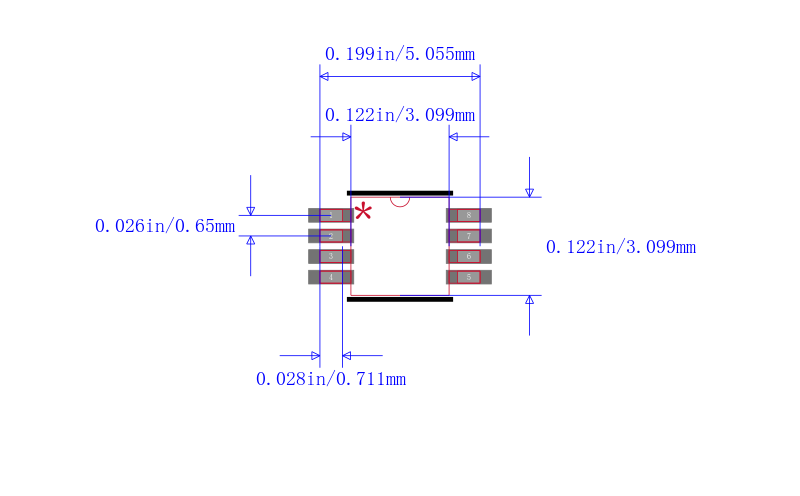

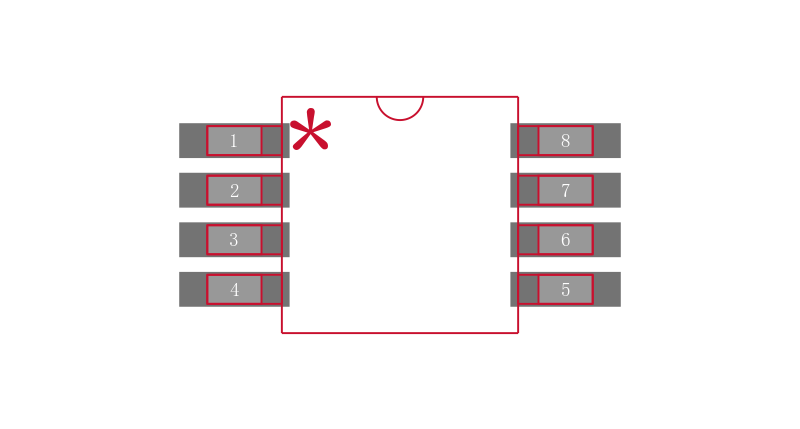

SN65LVDS9637DGKG4 TI 德州仪器 | 当前型号 | 当前型号 |

SN65LVDS9637DGK 德州仪器 | 完全替代 | SN65LVDS9637DGKG4和SN65LVDS9637DGK的区别 |

SN65LVDS9637DGKR 德州仪器 | 类似代替 | SN65LVDS9637DGKG4和SN65LVDS9637DGKR的区别 |