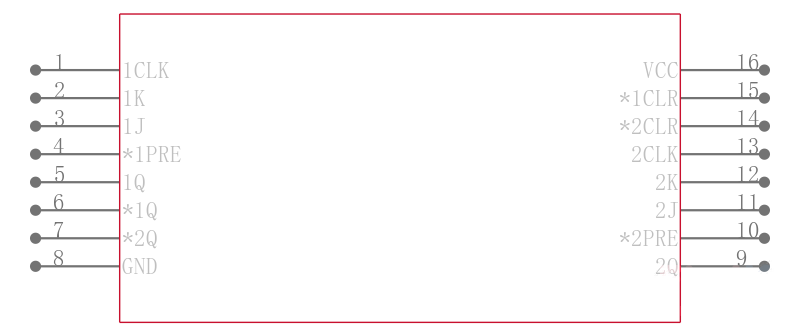

双J-负边沿触发触发器具有清零和预设 DUAL J-NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS WITH CLEAR AND PRESET

description/ordering information

The ’HC112 devices contain two independent J-K negative-edge-triggered flip-flops. A low level at the preset PRE or clear CLR inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive high, data at the J and K inputs meeting the setup time requirements are transferred to the outputs on the negative-going edge of the clock CLK pulse. Clock triggering occurs at a voltage

• Wide Operating Voltage Range of 2 V to 6 V

• Outputs Can Drive Up To 10 LSTTL Loads

• Low Power Consumption, 40-µA Max ICC

• Typical tpd = 13 ns

• ±4-mA Output Drive at 5 V

• Low Input Current of 1 µA Max

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

SNJ54HC112J TI 德州仪器 | 当前型号 | 当前型号 |

SN74HC112N 德州仪器 | 类似代替 | SNJ54HC112J和SN74HC112N的区别 |

SN74HC109N 德州仪器 | 类似代替 | SNJ54HC112J和SN74HC109N的区别 |

SN74HCT273DWR 德州仪器 | 功能相似 | SNJ54HC112J和SN74HCT273DWR的区别 |