IC,LATCH,SINGLE,8Bit,LV-CMOS,SOP,20Pin,PLASTIC

DESCRIPON/ORDERING INFORMATION

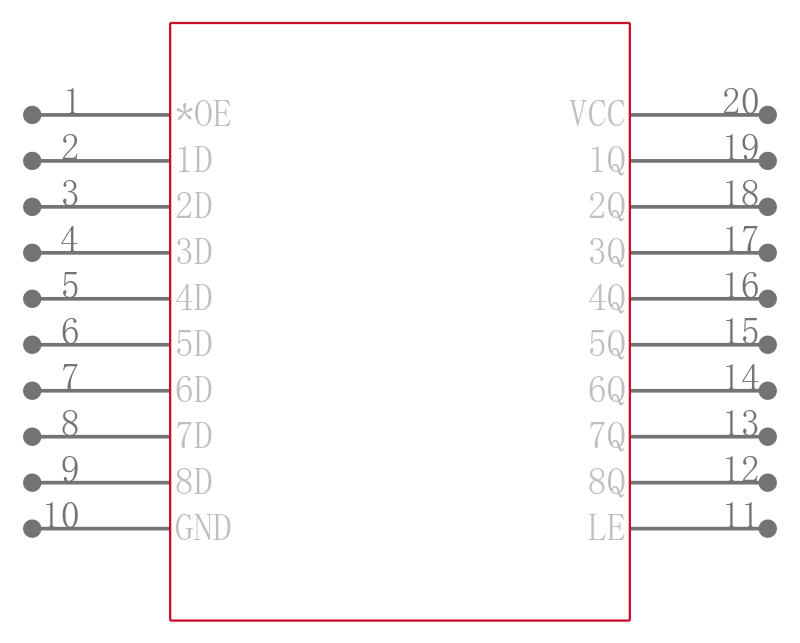

The SN74LV573AT is an octal transparent D-type latch. When the latch-enable LE input is high, the Q outputs follow the data D inputs. When LE is low, the Q outputs are latched at the logic levels of the D inputs.

A buffered output-enable OE input can be used to place the eight outputs in either a normal logic state high or low or the high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The high-impedance state and increased drive provide the capability to drive bus lines without interface or pullup components.

FEATURES

• Inputs Are TTL-Voltage Compatible

• 4.5-V to 5.5-V VCC Operation

• Typical tpd = 5.1 ns at 5 V

• Typical VOLP Output Ground Bounce

<0.8 V at VCC = 5 V, TA = 25°C

• Typical VOHV Output VOH Undershoot

>2.3 V at VCC = 5 V, TA = 25°C

• Supports Mixed-Mode Voltage Operation on All Ports

• Ioff Supports Partial-Power-Down Mode Operation

• Latch-Up Performance Exceeds 250 mA Per JESD 17

• ESD Protection Exceeds JESD 22

– 2000-V Human-Body Model A114-A

– 200-V Machine Model A115-A

– 1000-V Charged-Device Model C101