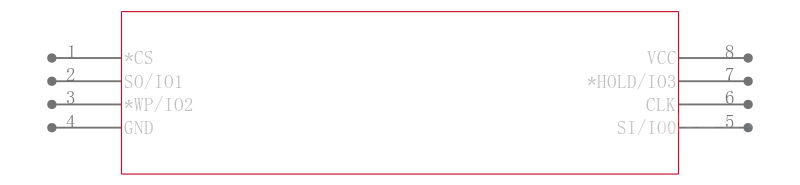

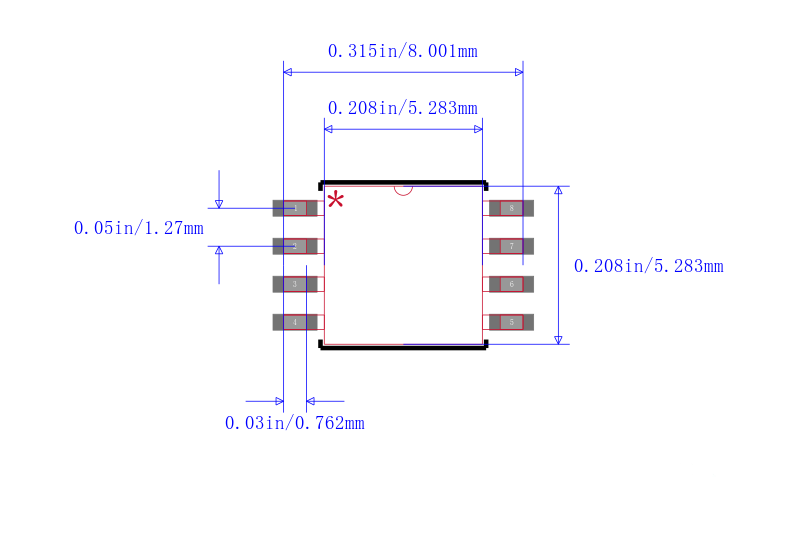

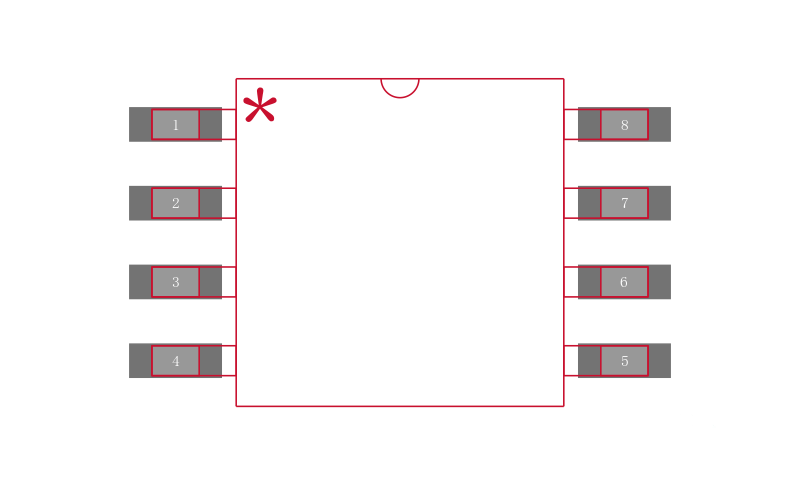

闪存, MirrorBit架构, 串行NOR, 128 Mbit, 16M x 8位, SPI, SOIC, 8 引脚

The Cypress S25FL127S device is a flash non-volatile memory product using: - MirrorBit technology that stores two data bits in each memory array transistor - Eclipse architecture that dramatically improves program and erase performance - 65 nm process lithography This device connects to a host system via a Serial Peripheral Interface SPI. Traditional SPI single bit serial input and output Single I/O or SIO is supported as well as optional two bit Dual I/O or DIO and four bit Quad I/O or QIO serial commands. This multiple width interface is called SPI Multi-I/O or MIO. The Eclipse architecture features a Page Programming Buffer that allows up to 128 words 256 bytes or 256 words 512 bytes to be programmed in one operation, resulting in faster effective programming and erase than prior generation SPI program or erase algorithms.

- .

- CMOS 3.0 Volt core

- .

- 128 Mbits 16 Mbytes

- .

- Serial peripheral interface SPI with multi-I/O

- .

- 100,000 program-erase cycles per sector, minimum

- .

- One Time Program OTP array of 1024 bytes

- .

- Cypress 65 nm MirrorBit Technology with Eclipse architecture

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

S25FL127SABMFV101 Cypress Semiconductor 赛普拉斯 | 当前型号 | 当前型号 |

S25FL127SABMFI101 赛普拉斯 | 类似代替 | S25FL127SABMFV101和S25FL127SABMFI101的区别 |