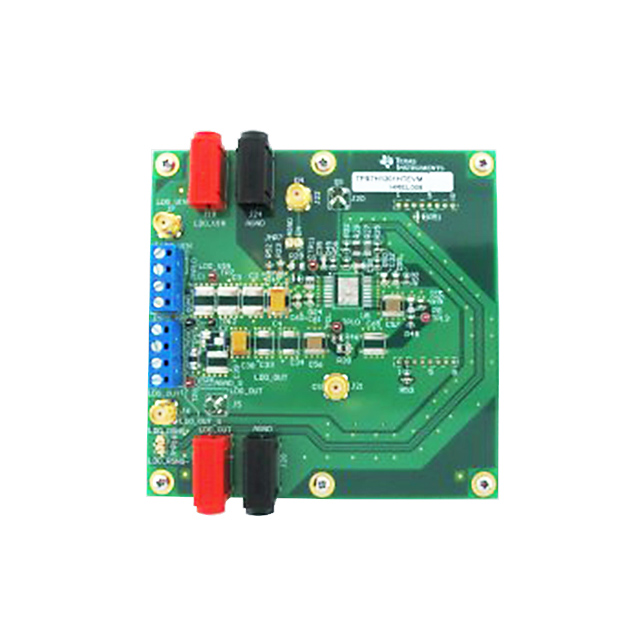

电源管理IC开发工具 TPS7H1201-HT Eval Module

The TPS7H1201-HT is a Ultra Low Dropout LDO linear regulator that uses a PMOS pass element configuration. The techniques employed allow for very low dropout. With an improved circuitry the TPS7H1201 operates under wide range of input voltage, from 1.5 V to 7 V which enables 6-V IN to 5-V OUT or 1.5-V IN to 1.2-V OUT voltage conversions for typical applications, while offering excellent PSRR.

The TPS7H1201 is ideally suited for high reliability applications. It features a very precise and programmable fold back current limit implementation with a very wide adjustment range.

To support complex requirements of FPGAs or DSPs, the TPS7H1201 provides programmable SoftStart and PowerGood output for easy power sequencing.

TPS7H1201 is available in a 16-pin ceramic flatpack package HKS.

An Application schematic is highlighted in Figure 1.

TPS7H1201HT uses ’s proprietary process to achieve low noise, high PSRR combined with high thermal performance in a 16-pin ceramic flatpack package HKS.

A number of features are incorporated in the design to provide high reliability and system flexibility. Current foldback, overload protection are incorporated in the design to make it viable for harsh environments.

also incorporates current limit protection. A resistor connected from Programmable Current limit PCL pin to ground sets the current limit activation point. When current limit set point is reached, output voltage will drop and output current will be maintained at the current limit set point.

A resistor connected from the CS current sense pin to VIN indicates voltage proportional to the output current, this feature can be used by the system to get voltage proportional to LDO output current

In order to provide system flexibility for demanding current needs, the LDO can be configured in parallel operation. This configuration will provide higher reliability MTBF for system needs due to reduced stress on the components, as the load current will be shared between the two LDOs. Alternately, it can also provide twice the output current to meet system needs as shown in Fig. 2.

An enable feature is incorporated in the design allowing one to enable or disable the LDO. If enabling / disabling the TPS7H1101SPEVM using enable pin, Vin voltage must be greater than 3.5V.

TPS7H1201HTEVM can also be disabled via SS pin. Pulling soft start SS pin low shall disable the EVM.

Power Good, an open drain connection, indicates the status of the output voltage. These provide the customers system flexibility in monitoring and controlling the LDO operation.