16字节FIFO的UART

UART IC 2, DUART Channel 16 Byte 48-TQFP 7x7

得捷:

IC DUAL UART 16BYTE FIFO 48-TQFP

立创商城:

TL16C2550IPFBR

德州仪器TI:

1.8-V to 5-V Dual UART with 16-Byte FIFOs

艾睿:

UART 2-CH 16Byte FIFO 1.8V/2.5V/3.3V/5V 48-Pin TQFP T/R

安富利:

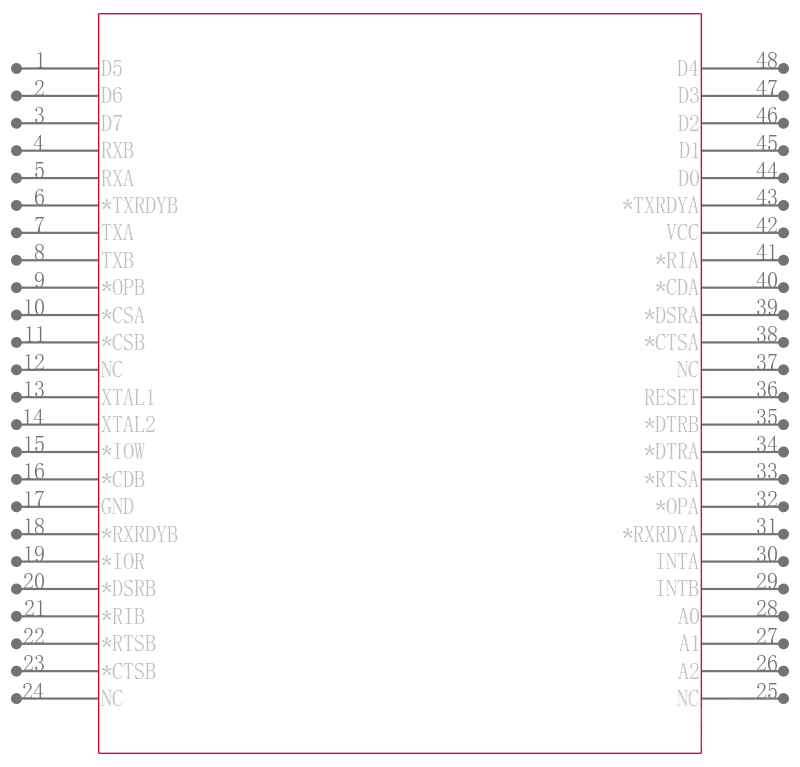

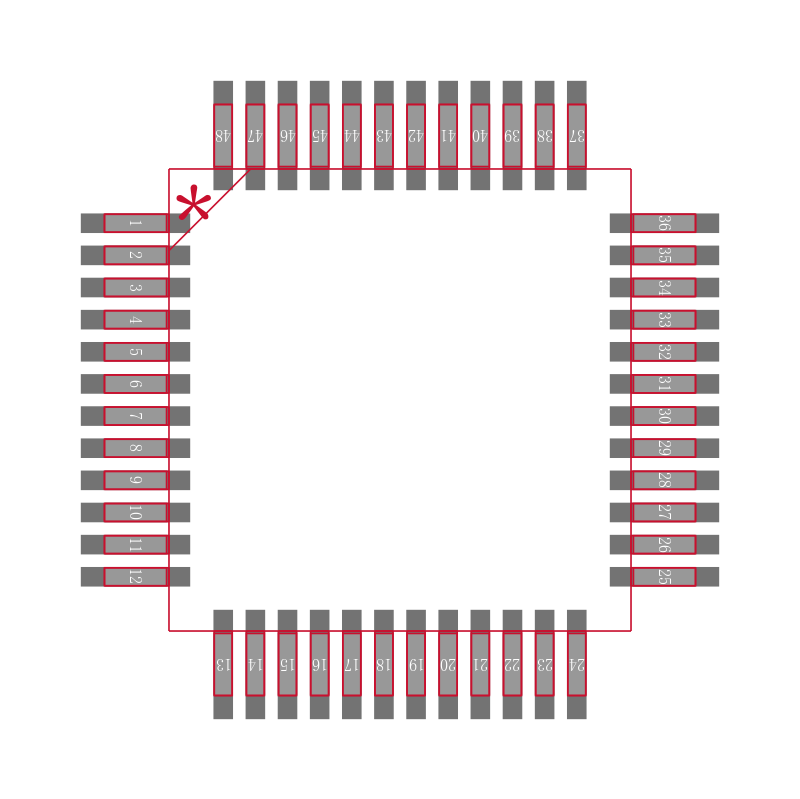

The TL16C2550 is a dual universal asynchronous receiver and transmitter UART. It incorporates the functionality of two TL16C550D UARTs, each UART having its own register set and FIFOs. The two UARTs share only the data bus interface and clock source, otherwise they operate independently. Another name for the uart function is Asynchronous Communications Element ACE, and these terms will be used interchangeably. The bulk of this document describes the behavior of each ACE, with the understanding that two such devices are incorporated into the TL16C2550.Each ACE is a speed and voltage range upgrade of the TL16C550C, which in turn is a functional upgrade of the TL16C450. Functionally equivalent to the TL16C450 on power up or reset single character or TL16C450 mode, each ACE can be placed in an alternate FIFO mode. This relieves the CPU of excessive software overhead by buffering received and to be transmitted characters. Each receiver and transmitter store up to 16 bytes in their respective FIFOs, with the receive FIFO including three additional bits per byte for error status. In the FIFO mode, a selectable autoflow control feature can significantly reduce software overload and increase system efficiency by automatically controlling serial data flow using handshakes between the RTS\ output and CTS\ input, thus eliminating overruns in the receive FIFO.Each ACE performs serial-to-parallel conversions on data received from a peripheral device or modem and stores the parallel data in its receive buffer or FIFO, and each ACE performs parallel-to-serial conversions on data sent from its CPU after storing the parallel data in its transmit buffer or FIFO. The CPU can read the status of either ACE at any time. Each ACE includes complete modem control capability and a processor interrupt system that can be tailored to the application.Each ACE includes a programmable baud rate generator capable of dividing a reference clock with divisors from 1 to 65535, thus producing a 16× internal reference clock for the transmitter and receiver logic. Each ACE accommodates up to a 1.5-Mbaud serial data rate 24-MHz input clock. As a reference point, that speed would generate a 667-ns bit time and a 6.7-µs character time for 8,N,1 serial data, with the internal clock running at 24 MHz.Each ACE has a TXRDY\ and RXRDY\ output that can be used to interface to a DMA controller.

Chip1Stop:

UART 2-CH 16Byte FIFO 1.8V/2.5V/3.3V/5V 48-Pin TQFP T/R

Verical:

UART 2-CH 16byte FIFO 1.8V/2.5V/3.3V/5V 48-Pin TQFP T/R

力源芯城:

双路带16字节FIFO的UART

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

TL16C2550IPFBR TI 德州仪器 | 当前型号 | 当前型号 |

TL16C2550IPFB 德州仪器 | 完全替代 | TL16C2550IPFBR和TL16C2550IPFB的区别 |

TL16C2550IRHB 德州仪器 | 类似代替 | TL16C2550IPFBR和TL16C2550IRHB的区别 |

TL16C550CFN 德州仪器 | 功能相似 | TL16C2550IPFBR和TL16C550CFN的区别 |