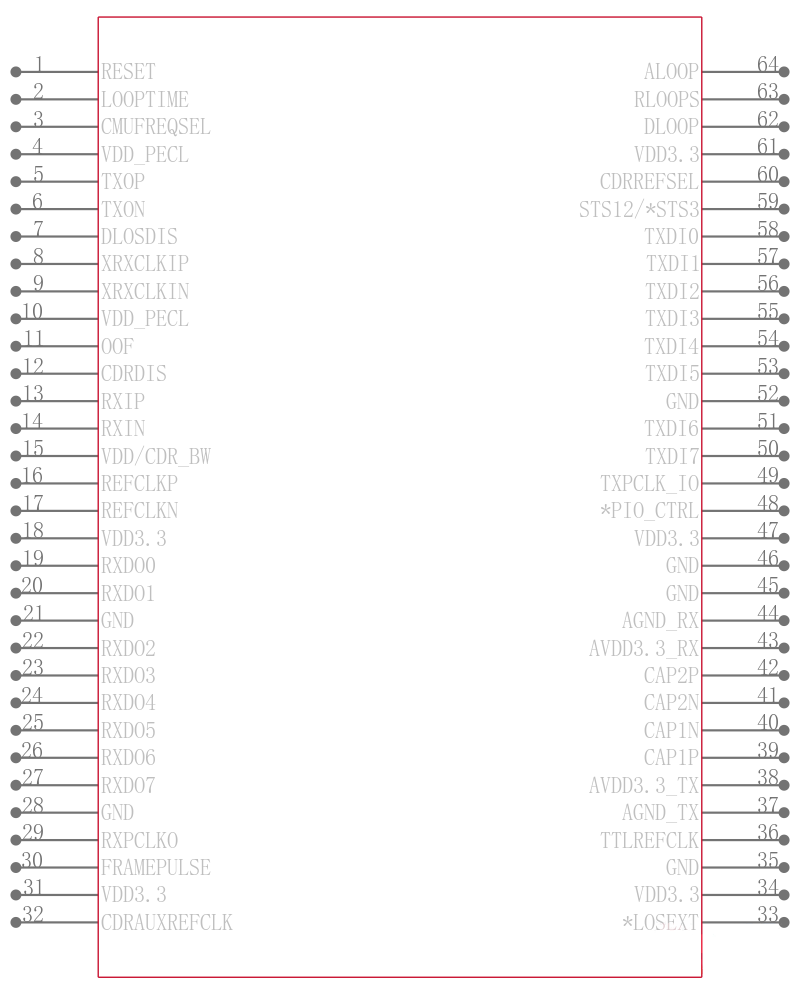

EXAR XRT91L30IQ-F 芯片, 收发器, OC12, 8位, 64QFP

GENERAL DESCRIPTION

The XRT91L30 is a fully integrated SONET/SDH transceiver for SONET/SDH 622.08 Mbps STS-12/ STM-4 or 155.52 Mbps STS-3/STM-1 applications. The transceiver includes an on-chip Clock Multiplier Unit CMU, which uses a high frequency Phase Locked Loop PLL to generate the high-speed transmit serial clock from a slower external clock reference. It also provides Clock and Data Recovery CDR function by synchronizing its on-chip Voltage Controlled Oscillator VCO to the incoming serial data stream. The internal CDR unit can be disabled

FEATURES

• Targeted for SONET STS-12/STS-3 and SDH STM-4/STM-1 Applications

• Selectable full duplex operation between STS-12/STM-4 standard rate of 622.08 Mbps or STS-3/STM-1 155.52 Mbps

• Single-chip fully integrated solution containing parallel-to-serial converter, clock multiplier unit CMU, serial-to-parallel converter, clock data recovery CDR functions, and a SONET/SDH frame and byte boundary detection circuit

• Ability to disable and bypass onchip CDR for external based received reference clock recovery thru Differential LVPECL input pins XRXCLKIP/N

• 8-bit LVTTL parallel data bus paths running at 77.76 Mbps in STS-12/STM-4 or 19.44 Mbps in STS-3/STM-1 mode of operation

• Uses Differential LVPECL or Single-Ended LVTTL CMU reference clock frequencies of either 19.44 MHz or 77.76 MHz for both STS-12/STM-1 or STS-3/STM-1 operations

• Optional use of 77.76 MHz Single-Ended LVTTL input for independent CDR reference clock operation

• Able to Detect and Recover SONET/SDH frame boundary and byte align received data on the parallel bus

• Diagnostics features include LOS monitoring and automatic received data mute upon LOS

• Provides Local, Remote and Split Loop-Back modes as well as Loop Timing mode

• Optional flexibility to re-configure the transmit parallel bus clock output to a clock input and accept timing signal from the framer/mapper device to permit the framer/mapper device time domain to be synchronized with the transceiver transmit timing.

• Meets Telcordia, ANSI and ITU-T G.783 and G.825 SDH jitter requirements including T1.105.03 - 2002 SONET Jitter Tolerance specification, Bellcore TR-NWT-000253 and GR-253-CORE, GR-253 ILR SONET

Jitter specifications.

• Complies with ANSI/TIA/EIA-644 and IEEE P1596.3 3.3V LVDS standard, 3.3V LVPECL, and JESD 8-B LVTTL and LVCMOS standard.

• Operates at 3.3V Core with 3.3V I/O

• Less than 660mW in STS-3/STM-1 mode or 800mW in STS-12/STM-4 mode Typical Power Dissipation

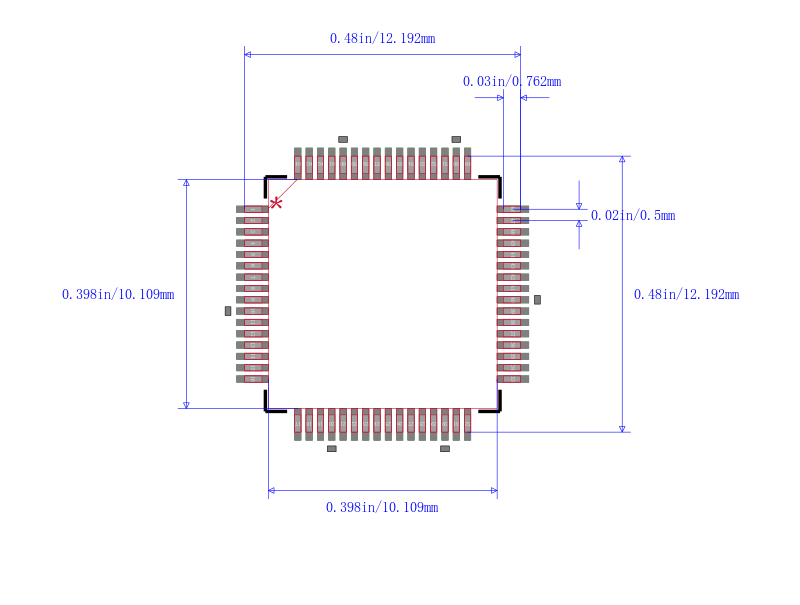

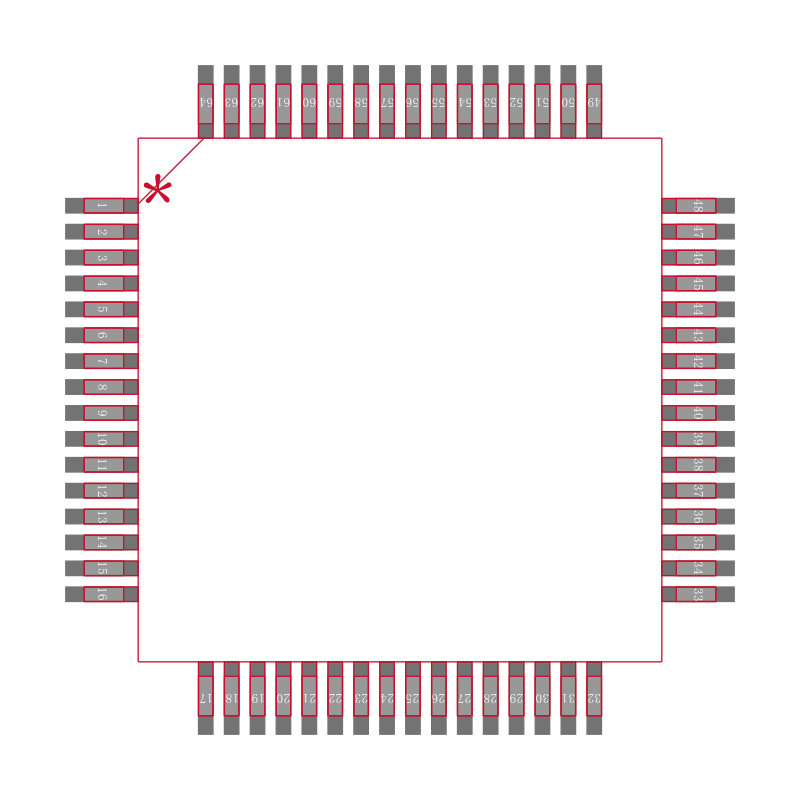

• Package: 10 x 10 x 2.0 mm 64-pin QFP

APPLICATIONS

• SONET/SDH-based Transmission Systems

• Add/Drop Multiplexers

• Cross Connect Equipment

• ATM and Multi-Service Switches, Routers and

Switch/Routers

• DSLAMS

• SONET/SDH Test Equipment

• DWDM Termination Equipment

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

XRT91L30IQ-F Exar Corporation 艾科嘉 | 当前型号 | 当前型号 |

XRT91L30IQ 艾科嘉 | 完全替代 | XRT91L30IQ-F和XRT91L30IQ的区别 |

XRT94L33IB-L 艾科嘉 | 功能相似 | XRT91L30IQ-F和XRT94L33IB-L的区别 |