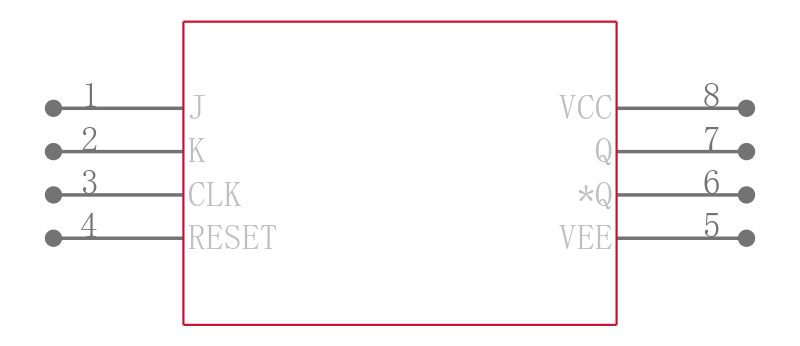

3.3V / 5V ECL JK触发器 3.3V / 5V ECL JK Flip−Flop

The MC10EP35 is a higher speed/low voltage version of the EL35 JK flip flop. The JK data enters the master portion of the flip flop when the clock is LOW and is transferred to the slave, and thus the outputs, upon a positive transition of the clock. The reset pin is asynchronous and is activated with a logic HIGH.The 100 Series contains temperature compensation.

Features

---

|

- .

- 410 ps Propagation Delay

- .

- Maximum Frequency > 3 GHz Typical

- .

- PECL Mode Operatio Range: VCC = 3.0 V to 5.5 V with VEE = 0 V

- .

- NECL Mode Operating Range: VCC = 0 V with VEE = -3.0V to -5.5V

- .

- Open Input Default State

- .

- Q Output will default LOW with inputs open or at VEE

- .

- Pb-Free Packages are Available

电源电压DC 5.00 V

无卤素状态 Halogen Free

电路数 1

时钟频率 3 GHz

位数 1

极性 Non-Inverting, Inverting

工作温度Max 85 ℃

工作温度Min -40 ℃

电源电压Max 5.5V, 5.5V

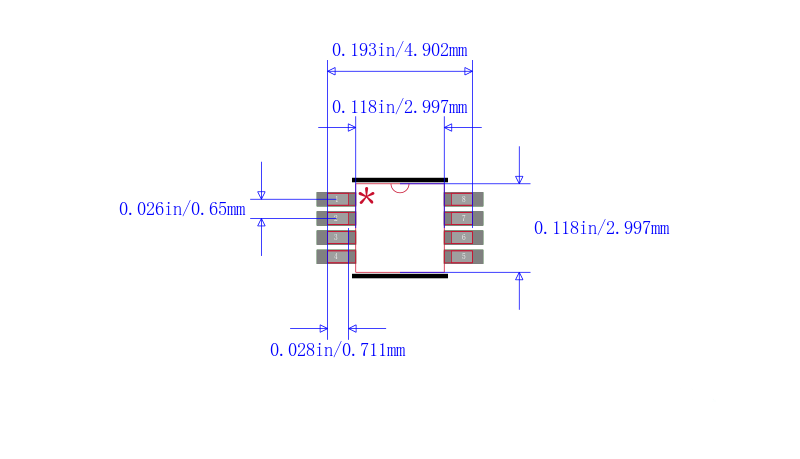

安装方式 Surface Mount

引脚数 8

封装 TSSOP-8

封装 TSSOP-8

工作温度 -40℃ ~ 85℃ TA

产品生命周期 Active

包装方式 Tape & Reel TR

制造应用 Using ECL Logic technologies for reducing system clock skew over the alternative CMOS and TTL technologies.

RoHS标准 RoHS Compliant

含铅标准 Lead Free

ECCN代码 EAR99

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

MC100EP35DTR2G ON Semiconductor 安森美 | 当前型号 | 当前型号 |

MC100LVEL51DTG 安森美 | 类似代替 | MC100EP35DTR2G和MC100LVEL51DTG的区别 |

MC10EP35DTR2G 安森美 | 类似代替 | MC100EP35DTR2G和MC10EP35DTR2G的区别 |