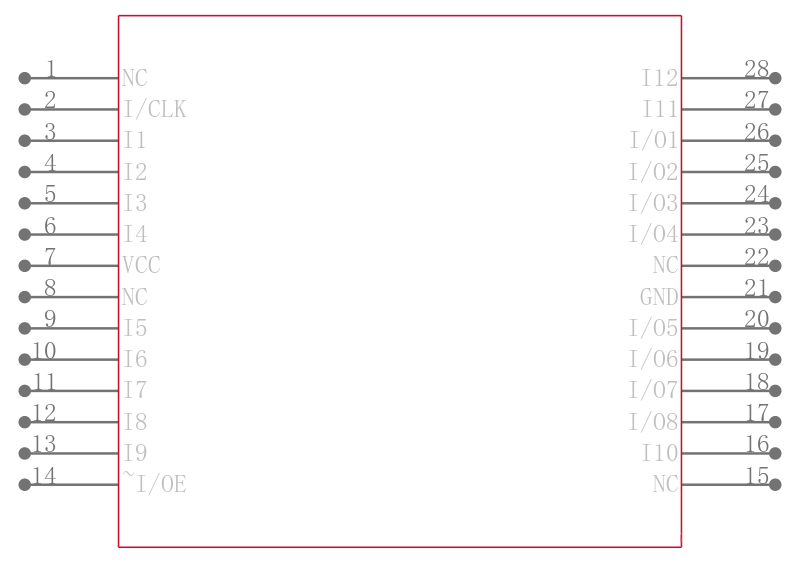

SPLD GAL Family 8 Macro Cells 80MHz 5V 28Pin PLCC

Description

The GAL20VP8, with 64 mA drive capability and 15 ns maximum propagation delay time is ideal for Bus and Memory control applications. The GAL20VP8 is manufactured using "s advanced E2CMOS process which combines CMOS with Electrically Erasable E2 floating gate technology. High speed erase times <100ms allow the devices to be reprogrammed quickly and efficiently.

Features

• HIGH DRIVE E2CMOS® GAL® DEVICE

— TTL Compatible 64 mA Output Drive

— 15 ns Maximum Propagation Delay

— Fmax = 80 MHz

— 10 ns Maximum from Clock Input to Data Output

— UltraMOS® Advanced CMOS Technology

• ENHANCED INPUT AND OUTPUT FEATURES

— Schmitt Trigger Inputs

— Programmable Open-Drain or Totem-Pole Outputs

— Active Pull-Ups on All Inputs and I/O pins

• E2 CELL TECHNOLOGY

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Yields

— High Speed Electrical Erasure <100ms

— 20 Year Data Retention

• EIGHT OUTPUT LOGIC MACROCELLS

— Maximum Flexibility for Complex Logic Designs

— Programmable Output Polarity

— Architecturally Compatible with Standard GAL20V8

• PRELOAD AND POWER-ON RESET OF ALL REGISTERS

— 100% Functional Testability

• APPLICATIONS INCLUDE:

— Ideal for Bus Control & Bus Arbitration Logic

— Bus Address Decode Logic

— Memory Address, Data and Control Circuits

— DMA Control

• ELECTRONIC SIGNATURE FOR IDENTIFICATION