MC100LVEP111: 2.5 V / 3.3 V 2:1:10 差分 ECL/PECL/HSTL 时钟/数据扇出缓冲器

The MC100LVEP111 is a low skew 2:1:10 differential driver, designed with clock distribution in mind, accepting two clock sources into an input multiplexer. The PECL input signals can be either differential or single-ended if the V output is used. HSTL inputs can be used when the LVEP111 is operating under PECL conditions.The LVEP111 specifically guarantees low output-to-output skew.Optimal design, layout, and processing minimize skew within a device and from device to device. To ensure tightest skew, both sides of differential outputs identically terminate into 50 ohms even if only one side is being used. When fewer than all ten pairs are used, identically terminate all the output pairs on the same package side whether used or unused. If no outputs on a single side are used, then leave these outputs open unterminated. This will maintain minimum output skew. Failure to do this will result in a 10-20 ps loss of skew margin propagation delay in the outputs in use.

Features

---

|

- .

- 85 ps Typical Device-to-Device Skew

- .

- 20 ps Typical Output-to-Output Skew

- .

- Jitter Less than 1 ps RMS

- .

- Additive RMS Phase Jitter: 60fs @156.25MHz, Typical

- .

- Maximum Frequency >3 Ghz Typical

- .

- VBB Output

- .

- 430 ps Typical Propagation Delay

- .

- The 100 Series Contains Temperature Compensation

- .

- PECL and HSTL Mode Operating Range: VCC = 2.375 V to 3.8 V with VEE = 0 V

- .

- NECL Mode Operating Range: VCC = 0 V with VEE = -2.375 V to -3.8 V

- .

- Open Input Default State

- .

- LVDS Input Compatible

无卤素状态 Halogen Free

输出接口数 10

电路数 1

工作温度Max 85 ℃

工作温度Min -40 ℃

电源电压 2.375V ~ 3.8V

安装方式 Surface Mount

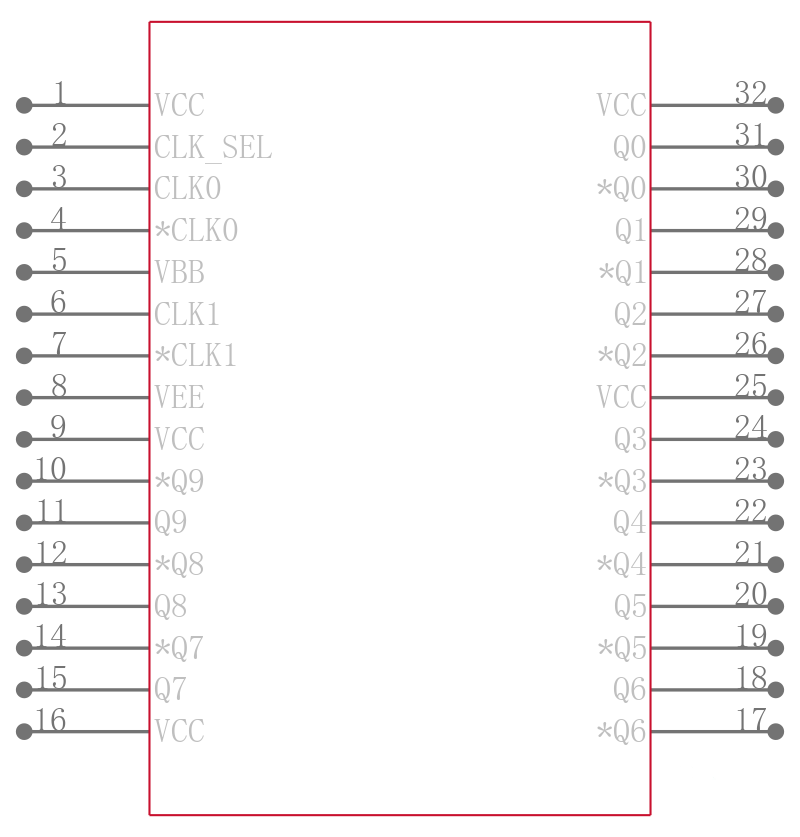

引脚数 32

封装 LQFP-32

封装 LQFP-32

工作温度 -40℃ ~ 85℃

产品生命周期 Active

包装方式 Tape & Reel TR

制造应用 General purpose clock and data distribution for Networking, ATE and Computing

RoHS标准 RoHS Compliant

含铅标准 Lead Free

ECCN代码 EAR99