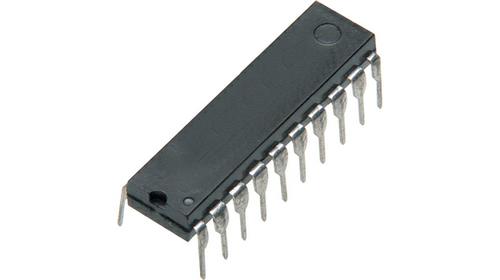

NXP 74HCT373N 芯片, 74HCT CMOS逻辑器件

The is a 3-state octal D-type Transparent Latch with high-speed Si-gate CMOS device and is pin compatible with low-power Schottky TTL. It is specified in compliance with JEDEC standard no-7A. It features separate D-type inputs for each latch and 3-state outputs for bus oriented applications. A latch enable LE input and an output enable OE input are common to all latches. The latch consists of eight D-type transparent latches with 3-state true outputs. When LE is high, data at the Dn inputs enters the latches. In this condition the latches are transparent, that is a latch output will change state each time its corresponding D input changes.

- .

- Common 3-state output enable input

- .

- ESD protection HBM JESD22-A114F exceeds 2000V

ESD sensitive device, take proper precaution while handling the device.

数字逻辑电平 CMOS

电源电压DC 5.00 V, 5.50 V max

输出电流 6 mA

电路数 8

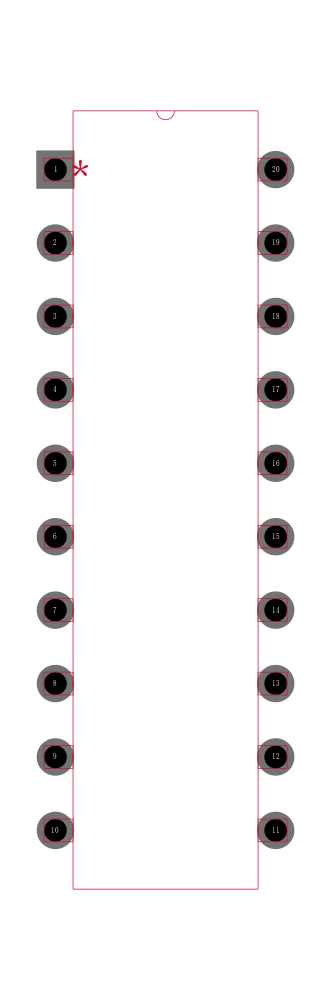

针脚数 20

位数 8

极性 Non-Inverting

逻辑门个数 8

工作温度Max 125 ℃

工作温度Min -40 ℃

电源电压Max 5.5 V

电源电压Min 4.5 V

安装方式 Through Hole

引脚数 20

封装 DIP

封装 DIP

产品生命周期 Unknown

包装方式 Bulk

制造应用 通信与网络, Communications & Networking

RoHS标准 RoHS Compliant

含铅标准 Lead Free

REACH SVHC标准 No SVHC

REACH SVHC版本 2015/12/17