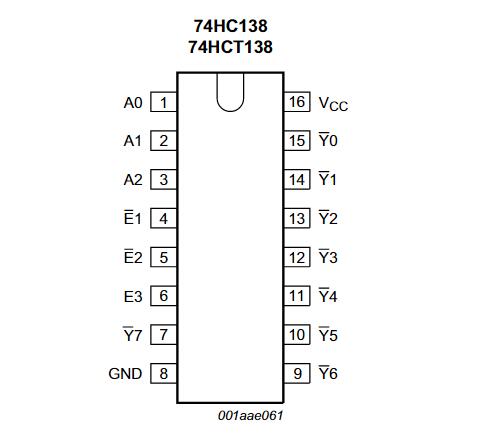

NXP 74HC138D 芯片, 74HC CMOS逻辑器件

The is a high speed Si-gate CMOS device and is pin compatible with low power Schottky TTL LSTTL. The 74HC138D decoder accepts three binary weighted address inputs A0, A1 and A3 and when enabled, provides 8 mutually exclusive active LOW outputs Y0 to Y7. This device features three enable inputs: two active LOW E1 and E2 and one active HIGH E3. Every output is HIGH unless E1 and E2 are LOW and E3 is HIGH. This multiple enable function allows easy parallel expansion to a 1-of-32 5 lines to 32 lines decoder with just four 74HC138D ICs and one inverter. This device can be used as an eight output demultiplexer by using one of the active LOW enable inputs as the data input and the remaining enable inputs as strobes. Permanently tie unused enable inputs to their appropriate active HIGH- or LOW-state.

- .

- Demultiplexing capability

- .

- Multiple input enable for easy expansion

- .

- Complies with JEDEC standard no. 7A

- .

- Ideal for memory chip select decoding

- .

- Active LOW mutually exclusive outputs

- .

- HBM EIA/JESD22-A114-F exceeds 2000V

- .

- MM EIA/JESD22-A115-A exceeds 200V

电源电压DC 2.00V min

输出接口数 8

电路数 1

针脚数 16

逻辑门个数 1

工作温度Max 125 ℃

工作温度Min -40 ℃

电源电压Max 6 V

电源电压Min 2 V

安装方式 Surface Mount

引脚数 16

封装 SOIC-16

封装 SOIC-16

工作温度 -40℃ ~ 125℃

产品生命周期 Unknown

包装方式 Cut Tape CT

制造应用 Clock & Timing, 消费电子产品, 机器人, Aerospace, Defence, Military, 国防, 军用与航空, 嵌入式设计与开发, 时钟与计时, Embedded Design & Development, Consumer Electronics, Robotics

RoHS标准 RoHS Compliant

含铅标准 Lead Free

REACH SVHC标准 No SVHC

军工级 Yes

REACH SVHC版本 2015/12/17

香港进出口证 NLR