NXP 74HC573N 芯片, 74HC CMOS逻辑器件

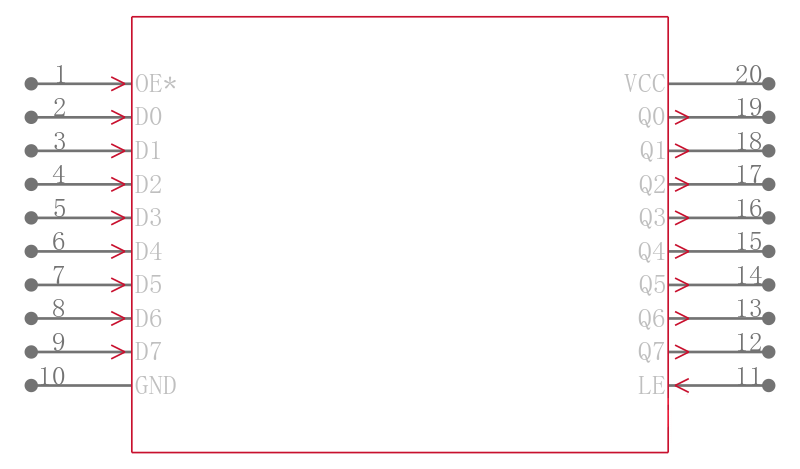

The is an octal D-type Transparent Latch with 3-state is a high-speed Si-gate CMOS device and is pin compatible with low-power Schottky TTL LSTTL . It is specified in compliance with JEDEC standard no-7A. The octal D-type transparent latch featuring separate D-type inputs for each latch and 3-state true outputs for bus-oriented applications. A latch enable LE input and an output enable OE input are common to all latches. When LE is high, data at the Dn inputs enter the latches. In this condition the latches are transparent, i.e. a latch output will change state each time its corresponding D-input changes. When LE is low the latches store the information that was present at the D-inputs a set-up time preceding the high-to-low transition of LE. When OE is low, the contents of the 8-latches are available at the outputs. When OE is high, the outputs go to the high-impedance OFF-state. Operation of the OE input does not affect the state of the latches.

- .

- CMOS input level

- .

- ESD protection HBM JESD22-A114F exceeds 2000V

ESD sensitive device, take proper precaution while handling the device.

电源电压DC 5.00 V, 6.00 V max

输出电流 7.8 mA

电路数 8

针脚数 20

位数 8

极性 Non-Inverting

逻辑门个数 8

工作温度Max 125 ℃

工作温度Min -40 ℃

电源电压Max 6 V

电源电压Min 2 V

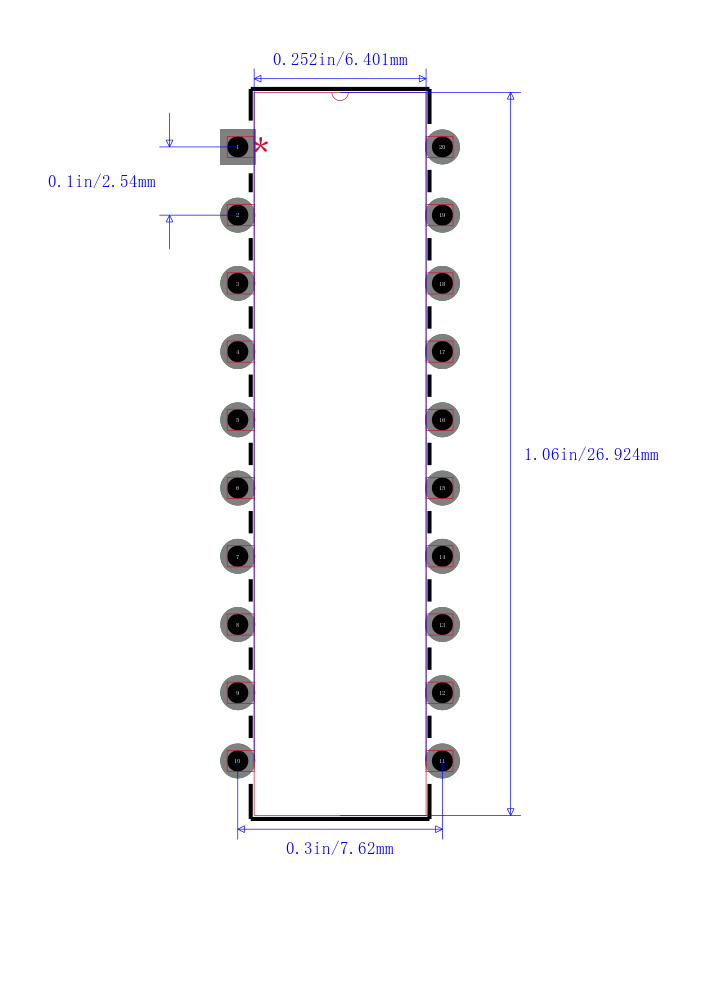

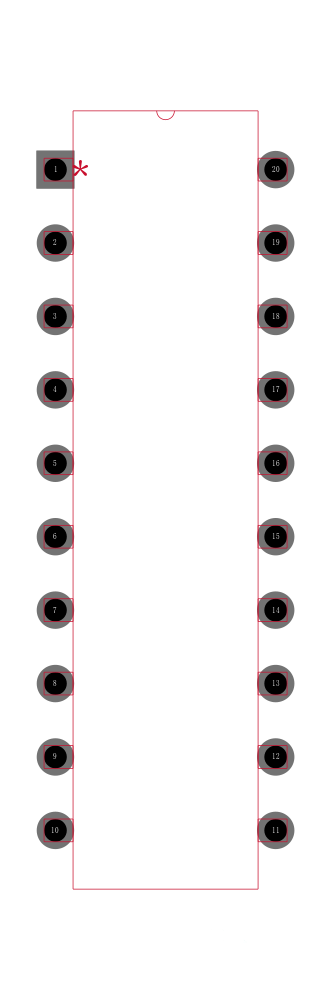

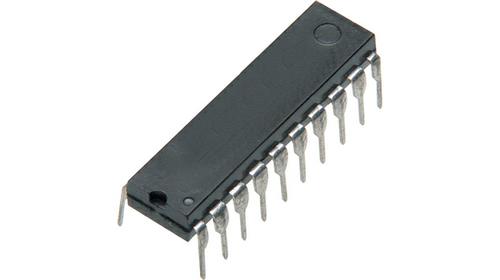

安装方式 Through Hole

引脚数 20

封装 DIP

封装 DIP

产品生命周期 Unknown

包装方式 Each

制造应用 Computers & Computer Peripherals, 计算机和计算机周边, Communications & Networking, 通信与网络

RoHS标准 RoHS Compliant

含铅标准 Lead Free

REACH SVHC标准 No SVHC

REACH SVHC版本 2015/12/17