1.2 GHz的时钟分配IC , PLL内核,分频器,延迟调整, 8路 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Eight Outputs

Product Details

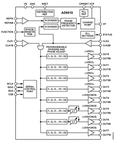

The provides a multi-output clock distribution function along with an on-chip phase-locked loop PLL core. The design emphasizes low jitter and phase noise to maximize data converter performance. Other applications with demanding phase noise and jitter requirements also benefit from this device.

The PLL section consists of a programmable reference divider R; a low noise, phase frequency detector PFD; a precision charge pump CP; and a programmable feedback divider N. By connecting an external voltage-controlled crystal oscillator VCXO or voltage-controlled oscillator VCO to the CLK2 and CLK2B pins, frequencies of up to 1.6 GHz can be synchronized to the input reference.

There are eight independent clock outputs. Four outputs are low voltage positive emitter-coupled logic LVPECL at 1.2 GHz, and four are selectable as either LVDS 800 MHz or CMOS 250 MHz levels.

Each output has a programmable divider that can be bypassed or set to divide by any integer up to 32. The phase of one clock output relative to another clock output can be varied by means of a divider phase select function that serves as a coarse timing adjustment. Two of the LVDS/CMOS outputs feature programmable delay elements with full-scale ranges up to 8 ns of delay. This fine tuning delay block has 5-bit resolution, giving 25 possible delays from which to choose for each full-scale setting Register 0x36 and Register 0x3A = 00000b to 11000b.

The AD9510 is ideally suited for data converter clocking applications where maximum converter performance is achieved by encode signals with subpicosecond jitter.

The AD9510 is available in a 64-lead LFCSP and can be operated from a single 3.3 V supply. An external VCO, which requires an extended voltage range, can be accommodated by connecting the charge pump supply VCP to 5.5 V. The temperature range is −40°C to +85°C.

**Applications**

- .

- Low jitter, low phase noise clock distribution

- .

- Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, and mixed-signal front ends MxFEs

- .

- High performance wireless transceivers

- .

- High performance instrumentation

- .

- Broadband infrastructure

### Features and Benefits

- .

- Low phase noise phase-locked loop core

- .

- Reference input frequencies to 250 MHz

- .

- Programmable dual modulus prescaler

- .

- Programmable charge pump CP current

- .

- Separate CP supply VCPS extends tuning range

- .

- Two 1.6 GHz, differential clock inputs

- .

- 8 programmable dividers, 1 to 32, all integers

- .

- Phase select for output-to-output coarse delay adjust

- .

- 4 independent 1.2 GHz LVPECL outputs

- .

- Additive output jitter of 225 fs rms

- .

- 4 independent 800 MHz low voltage differential signaling

- .

- LVDS or 250 MHz complementary metal oxide conductor

- .

- CMOS clock outputs

- .

- Additive output jitter of 275 fs rms

- .

- Fine delay adjust on 2 LVDS/CMOS outputs

- .

- Serial control port

- .

- Space-saving 64-lead LFCSP