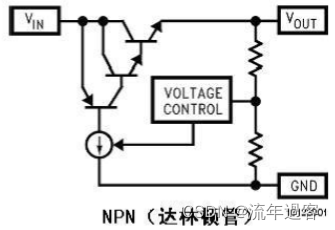

根据内部电路结构,线性稳压器主要分为以下几类: NPN、LDO、准LDO、PMOS、NMOS

以下是上述稳压器的电路原理: (1)NPN架构:  (2)LDO架构: (3)准LDO架构: (4)PMOS架构: (5)NMOS架构:

(2)LDO架构: (3)准LDO架构: (4)PMOS架构: (5)NMOS架构:

接下来以LDO以线性稳压器为例: 如上图所示,LDO管道由串联调整 VT 、取样电阻 R3 和 R4 、比较放大器 A 组成。

在比较器中加入取样电压 A 同相输入端与反相输入端的基准电压 Vref相比之下,两者之间的差值是放大器 A 放大后,控制串联调节管的压降,稳定输出电压。当输出电压 Vout 基准电压与取样电压的差值增加, 对比放大器输出的驱动电流增加,串联调节管压降降降低,使输出电压高。相反,如果输出电压 Vout 超过所需要的设定值, 比较放大器输出的前驱动电流减小, 从而降低输出电压。 在供电过程中, 连续进行输出电压校正, 调整时间仅限于比较放大器和输出晶体管回路的反应速度。

可调 LDO 一般输出电压计算公式: Vout=Vref(1 R2/R1) Iadj*R2* ;

Iadj 值很小,当 R2 值小时, IadjR2 值可以忽略不计。但如果是。 R2 值较大,那 IadjR2 值不容忽视。一般稳压器,如 1117系列的 Iadj 典型值在 50uA左右,如果 R2 取值为 2K 当电压误差达到时 0.1V 了。

一般 LDO 的 Vref 值为 1.25V,有些会有所不同。 ANACHIP 有一款AP133,其 Vref=0.8V,可用于调整输出介于 1~1.25V 这是普通的 LDO做不到。

η=Pout/Pin=(IoutVout)/(IinVin)=(Iout*V out)/((Iout Ignd)*Vin) 因为 Ignd 和 Iout 可以忽略不计,所以上式可以近似:

**η≈Vout/Vin** 可见 LDO 类似的效率等于输出电压比上的输入电压。 因此在选用 LDO 时,一定要注意输出电压和输入电压的压差。 在保证输出电压稳定的基础上, 输入电压越小,效率越高。特别是在大电流通路中,压差过大,不仅效率过低,而且热量过大,影响电路的稳定性。

近似计算公式:

由于结温升高会缩短芯片的使用寿命, 因此,我们必须尽可能降低芯片的温度,最好控制它 80~100℃内部;如果做不到这一点,至少要在产品规格书中标注最大工作温度。 80%以下。

:封装为 SOT-223的 117芯片,结到环境的热阻为 117℃/W(无散热器及通风措施) ,最大工作结温为 150℃。假设在40℃室温环境 ,IC 最大热损失约为: (150℃×0.8-40℃) / 117 ℃/W=0.68W

上述计算值何外部散热条件下的计算值, 印刷板上的铜箔在实际应用中会起到散热片的作用,因此实际能承受的耗散功率略大于上述计算值。

了解热损失 PD 和热阻θJA后,我们就能计算出温升的近似值,但这个值往往因印制板、 周围器件、 与实际温度不同的是度不同。 因此,有必要判断设计电路的温升是否能满足要求, 以实际测量的温度值为准。

Vdrop 为在某一输出电流强度下,输入输出压差的最小值。一般产品规格书上会提供相应的 Vdrop-Iout 曲线。

因此在实现 3.3V 转 2.5V 或 2.5V 转 1.8V 当输入输出压差相对较小时,必须注意使用 LDO 的 Vdrop 参数能否满足上述要求。

最小工作电压是指保证稳压器内部 IC 输入电压需要满足电路正常运行的最小值。因此,在设计中 Vin 除了要满足 V in -V out >V drop 外,还要满足 V in >V 最小工作 。

静态电流是指输入电源提供的稳压器工作电流,也称为接地电流。静态电流可以理解为提供稳压器 IC 正常运行的电流不直接携带,所以静态电流纯粹是损失,越小越好。

。因为线型稳压器是一个反馈系统, 一般是多极系统, 由于这些极点的存在, 相位裕度可能低于稳定状态的容限值,导致输出回路不稳定,甚至自激。

相位补偿技术通常用于改善相位裕度, 在系统内增加零点可以改善相位裕度,改善的效果取决于所增加的零点的频率位置。输出电路上并接的电容器, 其 ESR与电容器一起,可以在系统中增加零点, 相应的零点频率约为 1/(2πReC),其中 Re等效串联电阻, C 补偿电容值。 当补偿电容选择不当时,零点对相位裕度的改善不够,整个回路还是可能不稳定的。

在选择补偿电容时,我们需要关注电容 ESR 参数。

一般来说准 LDO 用电解电容输出补偿电容也能满足要求,但为了使用 ESR尽量小,电解容的容值不小于 47uF,推荐 47uF~100uF;输出小于等于 5V 电路的耐压值不小于 10V,推荐 10V~16V,大多数耐压值是为了使其更大 ESR 小些。对于 PNP LDO 来说,对 ESR要求会更严格。(现在有很多稳压器,因此,电容器用于外部补偿 ESR 要求变得不那么严格)在选择电容时,应参考芯片规格中关于输出电容的要求说明和建议参数值。

PSRR(Power Supply Rejection Ratio),, 采用对数比值, 单位为分贝,基本计算公式为: PSRR=20log[Ripple (Vin)/Ripple (Vout)]

: 可在芯片设计中进行 LDO 基准输出端一路增加低通滤波器。由于内置滤波器会占用较大的芯片尺寸, 因此,一些芯片在芯片外围电路上设计低通滤波器,引出基准脚(即 ),用于连接基准旁路电容。 增加旁路电容, 有利于降低输出噪声 ,提高 LDO 的 PSRR。但是旁路电容是对的 LDO 影响输出电压上升速度,旁路电容值越大,输出电压上升速率越慢,使用时应注意。陶瓷电容器的典型值为 470 pF ~ 1uF 。

该参数旨在保持输出稳压,导管上需要流过的最小电流。如果负载不符合最小负载电流的要求, 稳压器输出电压可能会浮动。 。

对于导管,调压电阻 R3 和R4 也是它的负载。因此,只要满足以下公式 LDO 保持电压稳定输出:

当 ILoad =0 只要满足 I R3 ≥I MiniLoad 可以,所以固定输出 LDO 在设计中,制造商可以通过调整 R3 和 R4的值来使 IC 内部可以满足最小负载电流的值, 用户在设计时不需要考虑这个参数。,R3 在外围电路的设计中,我们的用户在设计时需要考虑这个参数。

一般厂家除了提供最小负载电流的参数外,还会提供推荐的外围电路参数,方便我们设计时选择合适的电阻值。

应该严格参考Datasheet手册推荐布局,如下图所示为PCB上的LDO等效电路图: 理想的 LDO 版图设计,应该使 1、2、3、4 这四个环路做到尽可能的小。其中环路1 和环路 2 最重要: 因为,对输出纹波影响很大; , 还会影响补偿电容的等效 ESR,因为补偿电容的实际等效 ESR=ESRc +R trace ,当补偿电容与整个LDO 的环路变大时, R trace 变大,补偿电容的实际等效 ESR 也随之变大,从而会使整个电路变得不稳定; ; ,也要重视。