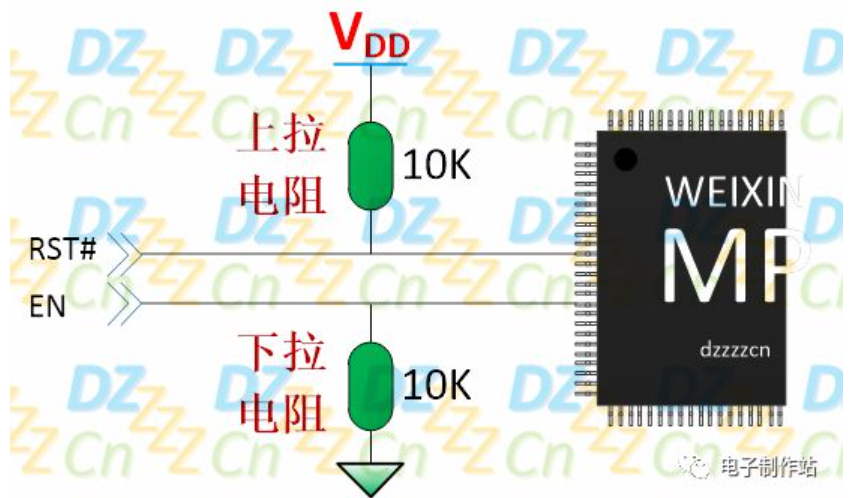

上拉(Pull Up )或下拉(Pull Down)电阻(统称拉电阻)最基本的功能是通过电阻将状态不确定的信号线夹在高电平(上拉)或低电平(下拉),不管它的具体用法如何,这个基本功能是一样的,但是在不同的应用场合,电阻的电阻要求会有所不同,这也导致了很多新的概念。本节我们将讨论这些内容。 如果拉电阻用于输入信号引脚,通常的功能是强制将信号线夹到某个电平,以防止信号线因悬挂而出现不确定状态,导致系统出现预期状态,如下图所示:

10.K欧姆的电阻是最常用的拉电阻。上拉电阻或下拉电阻的使用主要取决于电路系统本身的需要,例如,可以有效地控制信号(EN),我们希望电路系统上电后无效,使用下拉电阻。

假设能量信号用于控制电机,如果悬挂,信号线可能会被其他噪声干扰,误触发为高电平,导致电机不期望旋转,这当然不是我们想要的,此时可以增加下拉电阻。

而相应的,低有效复位控制信号(RST#),如果上电复位后无效,应使用上拉电阻。 大多数具有逻辑控制功能的芯片(如单片机,FPGA等)都会集成上拉或下拉电阻,用户可根据需要选择是否打开,STM32单片机GPIO模式包括上拉或下拉,如下图所示(来自ST数据手册:

根据拉电阻的阻值,我们也可以分为强拉或弱拉(weak pull-up/down),芯片内部集成的拉电阻通常较弱(电阻较大)。拉电阻越大,电平能力越小,抗外部噪声能力越小,拉电阻越小,相应的功耗越大,因为正常信号需要更多的能量来改变信号线的状态。拉电阻越小,电平能力越强(强拉),抵抗外部噪声的能力越强(也就是说,如果不期望干扰噪声改变强拉信号电平,必须相应加强所需能量),但 在能耗方面,拉电阻绝不会有偏差,如下图所示: 上拉电阻R1.每次控制信号降低L,都会产生控制信号VCC/R1.电流消耗(如果没有上拉电阻,电流为0),因此,对于下拉电阻R2.每次控制信号提高H也会产生VCC/R2R 电流消耗(本文假设高电平为VCC) 强拉和弱拉之间没有严格的区别。一般来说,我们使用的拉电阻是弱拉,因此我们仍然可以使用外部控制信号根据需要更改已经上下拉的信号线。 强拉电阻的极端是零欧姆电阻,即信号线直接连接到电源或地面。例如,对于EEPROM存储芯片24C如下图所示,02应用电路: 其中,E0,E1,E2(地址配置位置)在应用中,电源通常是直接强上拉的VCC,或强下拉到GND,由于存储芯片的地址在系统运行过程中不会再次改变,同样,芯片的写作控制引脚WC(Write Control)也被强下拉GND。

原文地址:https://mp.weixin.qq.com/s/OuOwLWp_s2b3ADeybT_7D