群友疑难杂症(加杨老师V信:PCB206 可入群):滤波电容为什么要靠近放置,储能电容为什么均匀放置?去耦半径是什么?滤波电容如何打孔?

杨老师回答:电容最小,谐振频率最高,去耦半径最小,所以放在最接近芯片的位置。此外,从自谐振频率点分析来看:我们知道自谐振频率点是区分电容器是容性还是感性的分界点。当电容器低于谐振频率时,电容器具有电容特性,高于谐振频率时,电容器具有电感特性。只有在自谐振频率点附近,电容器阻抗较低。因此,实际去耦电容器具有一定的工作频率范围,只有在自谐振频率点附近的频段内,电容才能具有良好的去耦效果,如果放置过远,超过去耦半径,就会失去去耦。

杨先生回答说:通常,芯片在设计时考虑到电源和引脚的排列位置,通常均匀分布在芯片的四个区域。因此,芯片周围存在电压扰动,整个芯片区域必须均匀去耦。如果不均匀放置,由于去耦半径的问题,芯片下部的电压扰动不能很好地去耦。

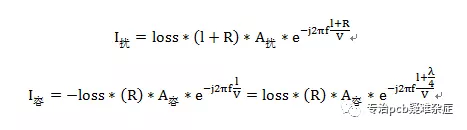

杨老师回答:一方面可以从公式入手,比较复杂,不容易理解

还有一种理解就是考察噪声源和电容补偿电流之间的相位关系。当芯片对电流的需求发生变化时,电压扰动会在电源平面的小局部区域产生。如果电容器想要补偿电流(或电压),则必须首先感知电压扰动。信号在介质中传播需要一定的时间,因此从局部电压扰动到电容感知的时间延迟。为了有效地传递补偿能量,噪声源与补偿电流的相位差应尽可能小,最好是相位。距离越近,相位差越小,补偿能量传递越多。

总之,去耦半径是可以计算的,可以在这个范围内工作。

评论:引出长线,然后连接孔,引入大寄生电感,尽量避免

评论:寄生电感减少,回流路径短,可接受

评论:寄生电感小,回流路径短,常规设计推荐。

点评:最佳打孔方式,但盘中孔设计不规范,加工成本增加,可靠性降低。

原作者:杨先生