时钟晶体电路通常是辐射发射的干扰源(EMI)

时钟晶体电路分为无源晶体电路和有源振荡电路:

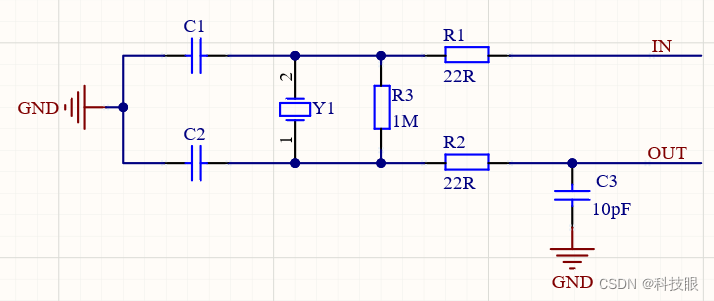

①.晶振串联电阻R1、R2通常用于防止晶体振动过度驱动。晶体振动过度驱动的结果是逐渐减少晶体振动的接触电镀,这将导致频率上升,并导致晶体振动的早期故障。drive level用于调整。用于调整drive level和发振余额。

②.晶体振动输入输出连接电阻R3功能是产生负反馈,确保放大器在高增益线性区域工作,一般在M欧级;并联电阻降低谐振阻抗,使谐振器易于启动;并联电阻值从100开始k-20M可正常振动,但会影响脉宽比。

③.晶振上并联的两个电容器C1、C2一般取值为20-30pf主要用于微调频率和波形,影响频率范围。

④.C电容器可以提高冲击信号的质量。

①.采用电源管脚LC滤波电路或Π滤波器电路,小电容器放电源管脚上,大电容器靠近小电容器,电磁珠的作用是防止振荡器的高频信号通过电源污染外部电路。

②.C电容器可以提高振荡器输出信号的质量。

③.晶体外壳应接地设计PCB在表面铺铜,将晶体外壳连接到地面。

④.输出采用始端串联阻抗匹配,阻值通常为10R、22R、33R等,根据实际情况调整其电阻,匹配时钟芯片附近的电阻。