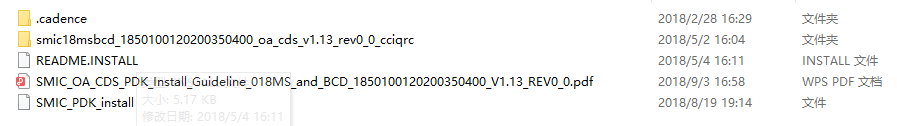

工艺文件包括: 安装脚本 脚本指南的安装 ReadME.INSTALL —script提示安装过程中的文件 smic18msbcd ---- 安装文件

在安装过程中,需要选择要安装的PDK选项: 1.EPI or Bulk The epi-seal encapsulation process [1, 2] is a unique wafer-level encapsulation for silicon structures that is free of contamination and native oxide. Such an encapsulation has been demonstrated to be crucial to achieving high stability [3, 4] with no observable fatigue [5, 6]. epi-seal包装工艺[1,2]是一种独特的硅结构晶片级包装,无污染和天然氧化物。这种包装已被证明是实现高稳定性的关键[3,4]

在安装过程中,需要选择要安装的PDK选项: 1.EPI or Bulk The epi-seal encapsulation process [1, 2] is a unique wafer-level encapsulation for silicon structures that is free of contamination and native oxide. Such an encapsulation has been demonstrated to be crucial to achieving high stability [3, 4] with no observable fatigue [5, 6]. epi-seal包装工艺[1,2]是一种独特的硅结构晶片级包装,无污染和天然氧化物。这种包装已被证明是实现高稳定性的关键[3,4]疲劳 [5,6]。 外延(Epitaxy, 简称Epi)工艺是指在单晶衬底上生长一层具有相同晶格排列的单晶材料,外延层可以是同质外延层(Si/Si),也可为异质外延层(SiGe/Si 或SiC/Si等);还有很多方法可以实现外延生长,包括分子束外延(MBE),超高真空化学气相沉积(UHV/CVD),常压及减压延伸(ATM RP Epi)等等。 外延生长是在单晶衬底(基板)上生长一层与衬底晶体相同的单晶层,就像原晶体向外延伸一段,因此称为外延生长。外延生长技术发展于20世纪50年代末60年代初。

据估计,在现代机械设备中,80~90%或部件损坏是由金属疲劳引起的。. 因为金属部件所受的外力超过一定限度,在材料内部抵抗最弱的地方,会出现人眼察觉不到的裂纹。 若零件受外力不变,小裂纹不会发育,材料也不易损坏。. 如果零件受到方向或大小经常重复变化的外力的影响,金属材料中的小裂纹有时会打开,有时会压缩,有时会相互研磨,从而扩大和发展裂纹。. 当裂纹扩大到一定程度,金属材料被削弱到无法承受外力时,只要有一点意外冲击,零件就会断裂。. 因此,金属疲劳造成的损伤往往是突然的,没有明显的迹象。. 金属疲劳一词最早是法国学者J·—V彭赛提出的。

参考:半导体外延生长的方式有哪些? [求助] Epi-Layer是Bulk CMOS工艺的option吗 目前商用的Bulk CMOS一般没有工艺Epi-layer,但如果你想要这个Layer, Foundry能提供什么工艺带来这个吗?Option呢,Tapeout成本会增加很多吗? 2.HRP 电阻选择 choose the type of HRP resistor:

- HRP 1k, HRP=1KOhm/Sq

- HRP 3k, HRP=3KOhm/Sq 在半导体芯片中,作为一种常备,常被设计成 SOI(Silicon on isolator,硅结构在绝缘体上 ),HRP(High Resistance Polysilicon,高阻值多晶硅电阻器 ) 是一种高阻值固定电阻器,HRP 采用多晶硅实现中硅结构,且 HRP 的多晶硅层与MOS 装置的栅极或 PIP(Poly-Si Isolator Poly-Si,多晶硅 - 绝缘体 - 多晶硅 ) 同时生成一层多晶硅,不需要在半导体芯片中制造。随着集成电路的不断升级,半导体芯片的尺寸、精度小,精度越来越高,响应速度越来越快,电路中度也越来越高。 但是由于HRP多晶硅厚度、CD(Critical Dimension, 关键尺寸 )、离子注入浓度等,因此很难稳定电阻值。特别是在大规模生产的半导体设备生产过程中,当多晶硅膜厚、面积大小、离子注入浓度等工艺程式不应改变时,各工艺步骤中的小变化对电阻值的影响是不可避免的 ( 例如,多晶硅层注入离子后,进行后续的积累掩护层工艺,由于掩护层膜的微小变化,多晶硅层的电阻值可能会变大或变小 ),半导体芯片成品 HRP 电阻值与所需目标值之间波动较大。 目前,HRP 电阻值的调整通常是通过改变离子注入多晶硅层的浓度或控制多晶硅层的大小来实现的,但这些动作往往只能根据半导体芯片成品的最终电气测试结果进行更大的调整 ( 例如,调整过程,但这种调整往往会导致调整错误 HRP 电阻值与所需目标值之间仍存在偏差,无法保证 HRP 电阻值的准确性 ),对于在线产品,由于动对电阻值的影响不可预测,在线产品束手无策。因此,行之有效的调整,将是HRP 将电阻值调整到目标值是量产阶段的重要任务。 参考:一种调节hrp电阻值的方法

一种调节 HRP 电阻值的方法,所述 HRP 至少包括多晶硅层,至少包括以下步骤 : 步骤 S1.监测多晶硅层,收集监测数据 ; 步骤 S2.根据监测数据进行估计 HRP 的电阻值 ; 步骤 S三、估计所述 HRP 当电阻值与目标值不同时,在半导体芯片的在线生产过程中,在多晶硅层上形成覆盖层,并根据估计 HRP电阻值,调节掩蔽层的透光率,使所述 HRP电阻值达到目标值。 通过收集在线监测多晶硅层的关键尺寸数据和离线监测多晶硅层的电阻值数据,估计 HRP 预估的电阻值HRP 当电阻值偏离目标值时,在半导体芯片的在线生产过程中及时调整 HRP 从而提高半导体芯片的稳定性。

3.MIM电容 Please choose the MIM density:

- MIM 1, Cspec=1fF/um^2

- MIM 2, Cspec=2fF/um^2

参考:科普:MOM,MIM和MOS电容器有什么区别? 对于CMOS一般来说,集成电容工艺MIM, MOM和MOS电容三类。MIM和MOM电容二端为金属,线性高,可用于OPA补偿电容等,MOS电容器一般需要一端接地或电源,线性度差,一般用于大电容滤波器。 MIM电容(Metal-Insulator-Metal):MIM电容器主要利用不同层金属及其介质形成。MIM电容相当于平行板电容,顶层二层金属间距较大,形成的电容值较小,MIM电容器一般由顶层二层金属和中间特殊金属层组成,MIM电容结构如下,CTM和Mt-中间介质层薄,形成的电容密度高,顶层寄生小,精度高。 MIM电容器的优点:可用Via奇数层与特殊工艺分别连接(M9, M7, M5)和偶数层 (M8,M6, M4)连接,可增加单位面积电容。 MIM缺点:65nm即使在工艺下使用9层金属和Poly去构建MIM,其单位面积只有电容(1).4fF寄生电容/微米平方)Cp可以达到总电容的10%。

4.Top metal顶层金属层数 Please choose the number of Top metal layers:

-

1 Top Metal

-

2 Top Metal Enter 1, 2…: 2 请问TM、TM1、TM2和UTM这几种top metal有什么区别?为什么有的只用一层顶金,有的只用两层顶金?一般只有吗?RF只有在工艺中绘制电感时才能使用utm? 数字电路,通常一层稍厚的顶层金属就足够了。例如,一层8K的TM 特别是模拟电路RF大多数情况下,电路需要一层厚度来制造电感等无源设备,如34K的TM2(也叫UTM),有时候选择再次TM下面加一层厚,TM1,比如8K左右。可以用来做power gnd之类的routing。 是不是两层厚金的工艺,比如smic13_1p8m_2tm这是它的顶层TM2一定就是UTM呢?也就是说TM2和UTM是不是就是一个意思啊? 后道工艺不同,厚度和材质不同。RF画电感用utm更多。但是我明白这个也应该用于大电流。 若安装工艺为1P6M,有TM1,MTT2两层top metal,画版图图的时候LSW窗口中选择M5或者选TM1画出来的是不是都是TM1层?还是说两者不一样,TM1是厚一点的M5,谢谢 安装目录下应该有文档会告诉你的吧,还有安装的时候应该也是让选了金属厚度的,对SMIC的工艺不熟悉,只能建议你看看文档里面怎么 不是的吧 IP6M 是最高metal层次是metal6 MT1 相当于metal7 MTT2相当于metal 8吧。 对于TM, RF客户也可以选择2个顶部金属层工艺。1"顶金属(TM1)必须遵循逻辑标准顶金属设计规则,2d顶金属(TM2)必须遵循MS&RF厚顶金属设计规则。两个顶部通过TV1和TV2)遵循逻辑标准顶部通过设计规则。两个顶部金属层工艺不能与堆叠的MIM(7.2.5)一起使用。 SMIC提供的文档有说明,选择不同厚度的顶铝,用的顶铝层次不同

参考:[1]Top metal_eetop [2][求助] 请问TM、TM1、TM2和UTM这几种top metal的区别? [3][求助] smic工艺top metal疑问

5.Please choose the MIM type:

- TYPE 1 (1st option), MIM is between thin top metal and Mn [Mn is the highest inter metal]

- TYPE 2 (2nd option), MIM is between Mn and Mn-1 [Mn is the highest inter metal] Enter 1, 2…: 2

6.Please choose the type of top metal for installation:

- 8K + 40K Top Metal Enter 1, 2…: 1 在铜线封装应用中。设计定方案的时侯,topmetal的厚度是否在选择工艺时选用最厚的?如有25k,40k,8k选择,不增加成本,只选最厚?就是最好的? 如果只走电源,当然厚的好;如果走信号,那就不一定了 要结合实际需求吧。如果只选最厚的,相应的DIE SIZE就会大呀。因为越厚的,design rule越大。得考虑成本吧。 8KTM – Top metal 厚度是 8K A 40KTM – Top metal 厚度 40K A , 就是所謂的 Thick Top Metal 参考:top metal的厚度问题 7.Please choose the number of inter metal layers:

- 4 inter metals Enter 1, 2…: 1 The PDK Package option you selected is: Epi_1P6M_TM1_MTT2_HRP3k_MIM2_TYP2

NOTICE: This PDK only contains RC extraction files for below metal options:

(1) 1P5M for 2 topmetal=8K+40k(1TM1_1MTT2), 2fF mim between M3 & M4 (mim2_ckt), HRP 3K

(2) 1P5M for 1 topmetal=33k(1TM2), 2fF mim between M3 & M4 (mim2_typ2_ckt), HRP 3K

(3) 1P6M for 2 topmetal=8K+40k(1TM1_1MTT2), 2fF mim between M3 & M4 (mim2_typ2_ckt), HRP 3K

(4) 1P6M for 1 topmetal=33k(1TM2), 2fF mim between M3 & M4 (mim2_typ2_ckt), HRP 3K

For other metal options, user can download RC files from SMICNOW,

or raise request if no such supply, we will deliver upon request.

NOTICE: Please run “virtuoso -nograph” command in terminal to debug if the cadence tool can’t be launched successfully!!! 1P6M: 1p: one poly 6m: six metal 这是基本知识。 1P6M和2P6M对比,两层poly和一层poly有什么区别: 2p就是有poly电容 要实现Poly-to-Poly电容,必须有两层Poly的CMOS结构。图1显示了Poly-to-Poly电容的结构示意图。 缺点:两层poly工艺,单位面积电容值小,底层poly和P-sub之间会形成大的寄生电容(已淘汰)。

参考:请问smic18mmrf_1P6M工艺库中的1P和6M是什么意思 [求助] 1P6M和2P6M