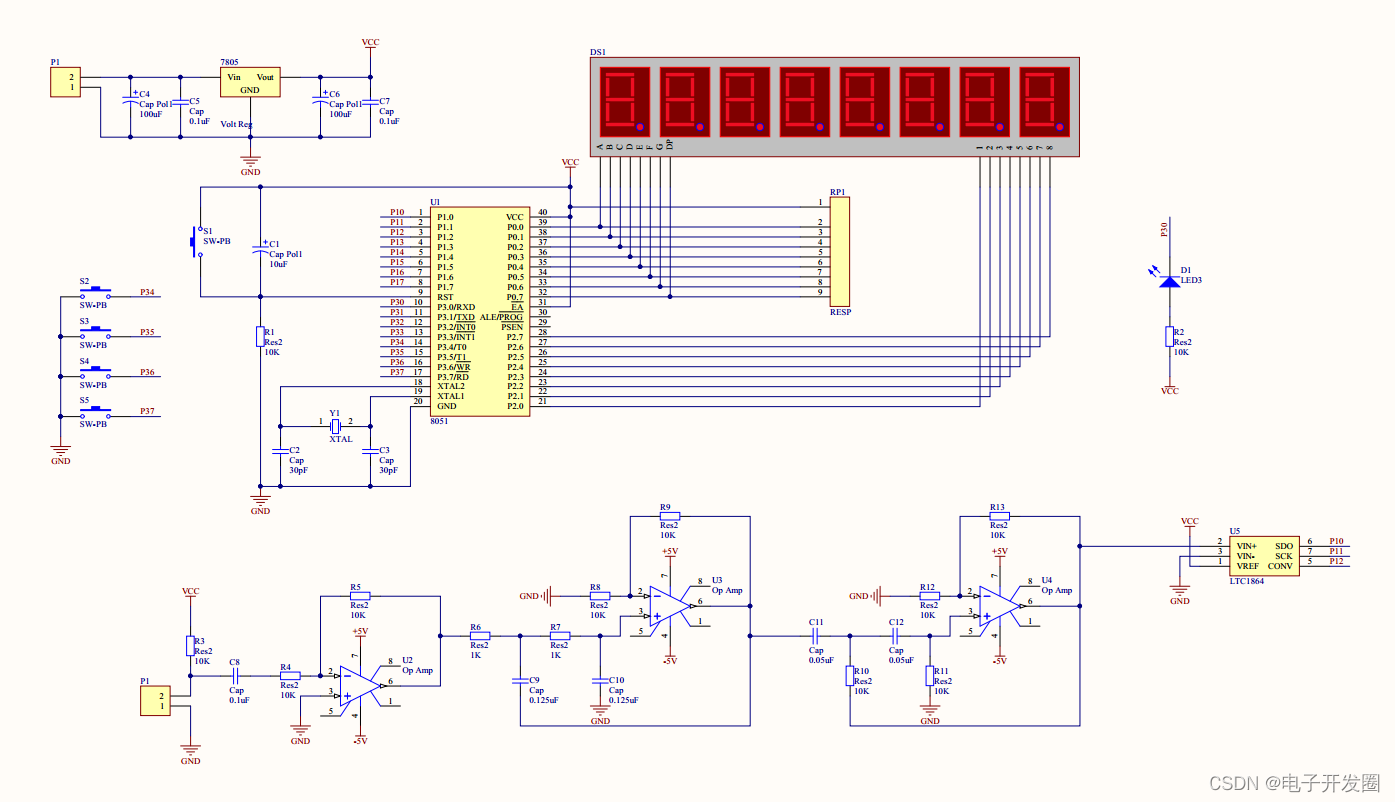

1.主控芯片采用51/52单片机; 实时分贝和报警阈值采用数字管显示; 3.噪声测量范围为40~100dB; 4、采用LM358芯片放大信号; 5、采用LTC1864模数转换; 报警阈值可通过按钮设置; 7.分贝超过阈值,LED报警灯亮;

采用AltiumDesigner作为电路设计工具。AltiumDesigner设计原理图,PCB绘制编辑、拓扑逻辑自动布线、信号完整性分析、设计输出等技术的完美集成,为设计师提供了新的设计解决方案,使设计师能够轻松设计,熟练使用该软件将大大提高电路设计的质量和效率。

单片机管脚说明:

P0端口(P0.0-P0.7):P0口为8位漏极开路双向I/O每个引脚可吸收8TTL门电流。当P第一次写1口管脚时,定义为高阻输入。P0可用于外部程序数据存储器,可定义为数据/地址的第八位。在FIASH编程时,P0 口作为原码输入口,当FIASH校验时,P此时输出原码P外部必须被拉高。

P1端口(P1.0-P1.7):P1口是提供内部上拉电阻的8位双向I/O口,P1口缓冲器接收输出4TTL门电流。P1口管脚写入1后,内部上拉为高电平,可作为输入,P由于内部上拉,1口被外部下拉为低电平时输出电流。FLASH编程和校准时,P第八位地址接收1口。

P2端口(P2.0-P2.7):P两口为8位双向双向,内部上拉电阻I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P当两口被写为1时,管脚被内部上拉电阻拉高,并作为输入。因此,作为输入,P2口管脚被外部拉下,输出电流。这是因为内部上拉。P存取外部程序存储器或16位地址外部数据存储器时,2口,P二口输出地址高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH在编程和位地址信号和控制信号进行编程和验证。

P3端口(P3.0-P3.7):P三口管脚是一个双向的,具有内部上拉电阻I/O端口可接收输出4个TTL门电流。当P三口写入1后,被内拉成高电平,用作输入。作为输入端,由于外部下拉为低电平,P三口输出电流(ILL)。P三口同时接收一些闪烁编程和编程验证的控制信号。

采用Proteus作为模拟设计工具。Proteus是一个名字EDA工具(仿真软件)从原理图布图、代码调试到单片机与外围电路协同仿真,一键切换PCB从概念到产品了从概念到产品的完整设计。

主程序设计

void main() { TMOD|=0X01; TH0=(65536-10000)/256; TL0=(65536-10000)%6; ET0=1.//打开定时器0中断允许 EA=1;//打开总中断 TR0=1;///打开定时器 while(1) { //显示 P0=smgduan0[xian/100]; smg1=0;delay(100);smg1=1; P0=smgduan1[xian0/10];smg2=0;delay(100);smg2=1; P0=smgduan0[xian]; smg3=0;delay(100);smg3=1; P0=smgduan0[limit/100]; smg5=0;delay(100);smg5=1; P0=smgduan1[limit0/10];smg6=0;delay(100);smg6=1; P0=smgduan0[limit]; smg7=0;delay(100);smg7=1; //按键检测 if(!k1) { if(limit<900) limit =10; while(!k1) { if(limit<900) limit =10; while(!k1); } if(!k2) { if(limit>0) limit-=10; while(!k2); } if(!k3) { if(limit<900) limit ; while(!k3); } if(!k4) { if(limit>0) limit--; while(!k4); } //报警 if(xian>limit) beep=0; else beep=1; } }源文件获取

关注微信官方账号-电子开发圈,首页发送“噪声” 获取;