对于串入并出以下是我个人的理解和实际开发工程中得出的经验

图一:

由我上图所画 可以得出 一个8位串入数据输入, 8位并行输出。可以看出先移的是高位,就是第一个位进去的到最后会在最高位。

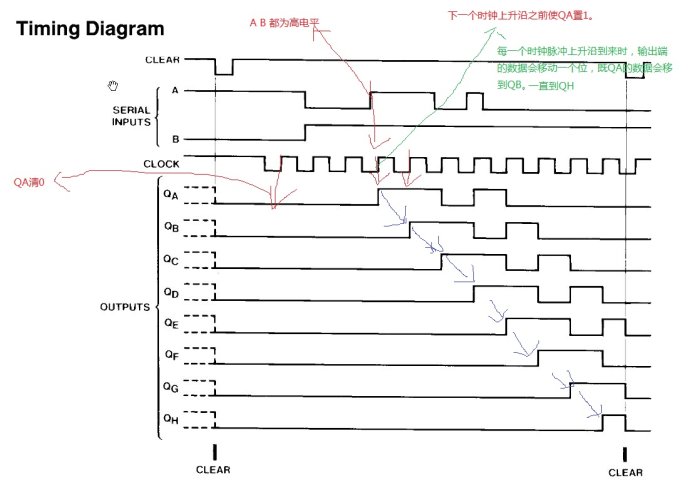

图为时序图

图为时序图

A

clean

clock 是时钟

由上图可以得出如果 A B 有一个为低电平 ,那么阻止新数据的进入,并在下一个时钟上升沿时,将 QA 端清0.

如果A

对于串入并出以下是我个人的理解和实际开发工程中得出的经验

图一:

由我上图所画 可以得出 一个8位串入数据输入, 8位并行输出。可以看出先移的是高位,就是第一个位进去的到最后会在最高位。

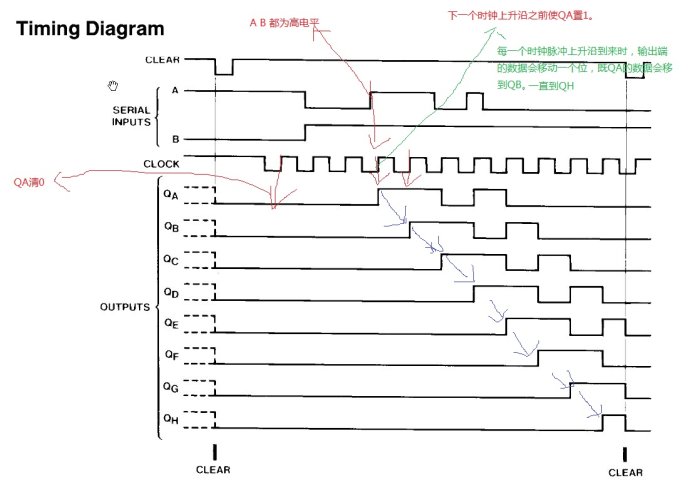

图为时序图

图为时序图

A

clean

clock 是时钟

由上图可以得出如果 A B 有一个为低电平 ,那么阻止新数据的进入,并在下一个时钟上升沿时,将 QA 端清0.

如果A