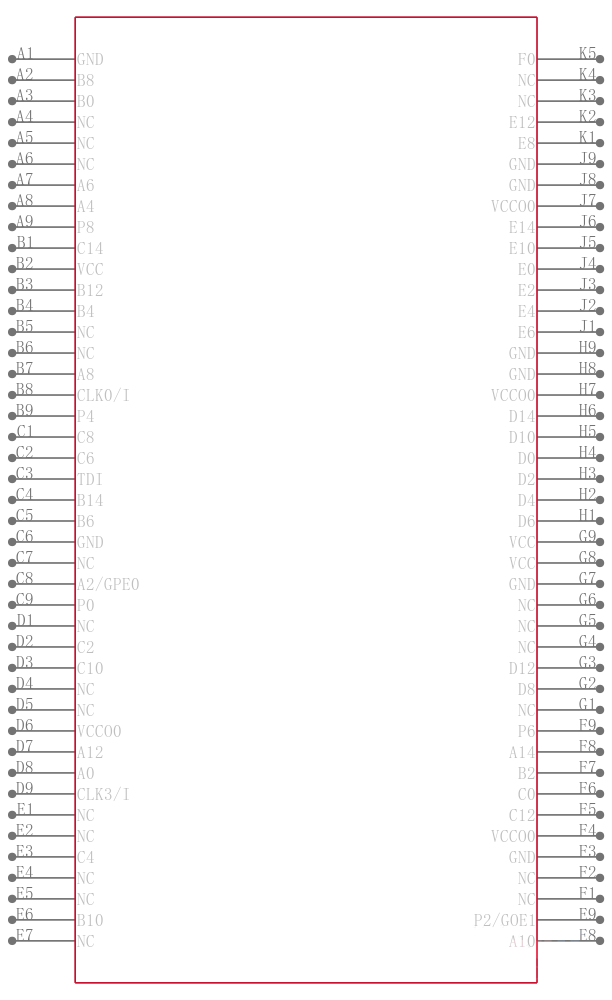

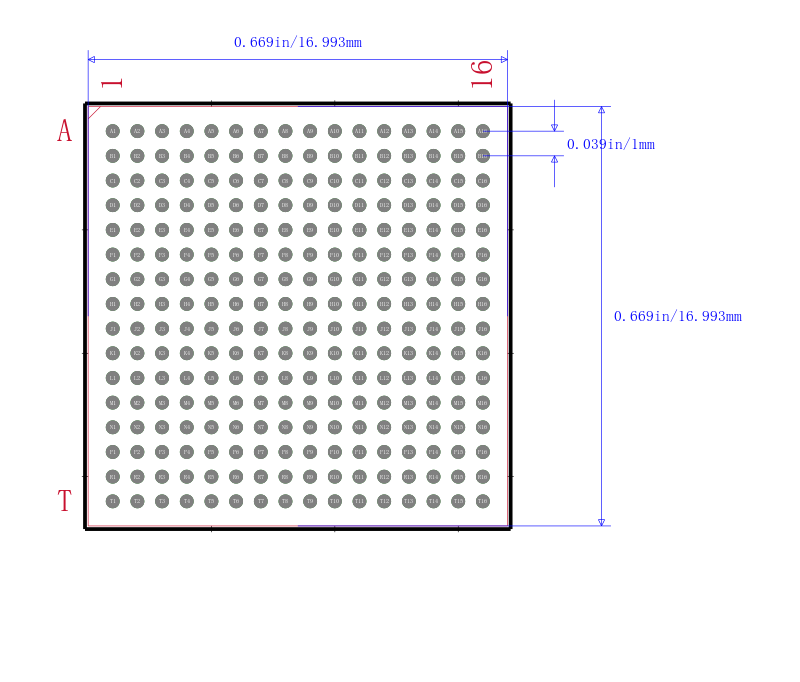

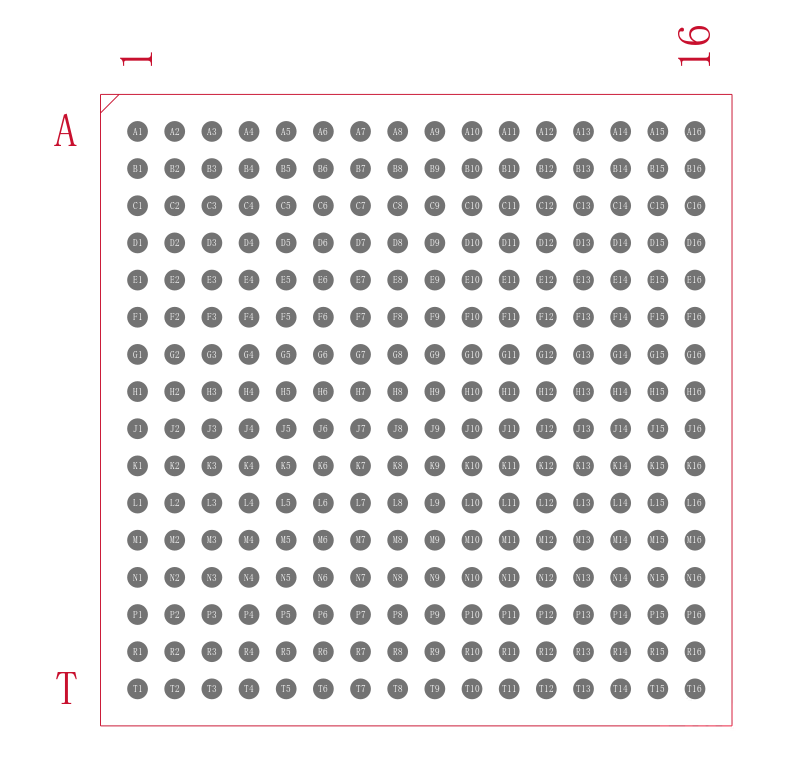

CPLD ispMACH® 4000B Family 256 Macro Cells 168MHz 2.5V 256Pin FBGA

* High Performance * fMAX = 400MHz maximum operating frequency * tPD = 2.5ns propagation delay * Up to four global clock pins with programmable clock polarity control * Up to 80 PTs per output * Ease of Design * Enhanced macrocells with individual clock, reset, preset and clock enable controls * Up to four global OE controls * Individual local OE control per I/O pin * Excellent First-Time-FitTM and refit * Fast path, SpeedLockingTM Path, and wide-PT path * Wide input gating 36 input logic blocks for fast counters, state machines and address decoders * Zero Power ispMACH 4000Z and Low Power ispMACH 4000V/B/C * Typical static current 10µA 4032Z * Typical static current 1.8mA 4000C * 1.8V core low dynamic power * Broad Device Offering * Multiple temperature range support * Commercial: 0 to 90°C junction Tj * Industrial: -40 to 105°C junction Tj * Automotive: -40 to 130°C junction Tj * Easy System Integration * Operation with 3.3V, 2.5V or 1.8V LVCMOS I/O * Operation with 3.3V 4000V, 2.5V 4000B or 1.8V 4000C/Z supplies * 5V tolerant I/O for LVCMOS 3.3, LVTTL, and PCI interfaces * Hot-socketing * Open-drain capability * Input pull-up, pull-down or bus-keeper * Programmable output slew rate * 3.3V PCI compatible * IEEE 1149.1 boundary scan testable * 3.3V/2.5V/1.8V In-System Programmable ISP™ using IEEE 1532 compliant interface * I/O pins with fast setup path