MC100EP195B 系列 3.3 V ECL 可编程延时芯片 - QFN-32

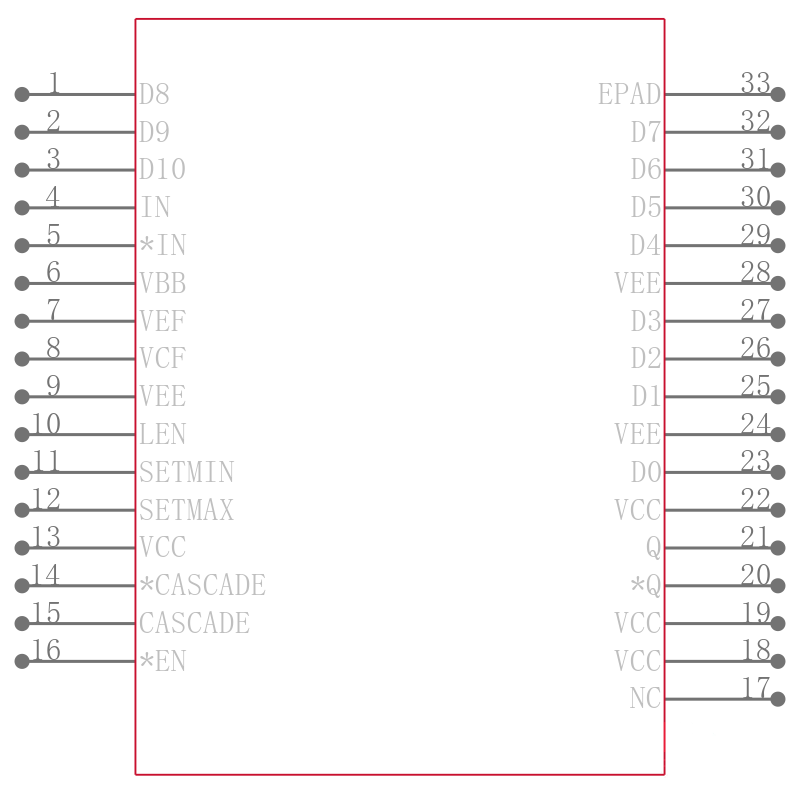

The MC100EP195B is a Programmable Delay Chip PDC designed primarily for clock deskewing and timing adjustment. It provides variable delay of a differential NECL/PECL input transition. The delay section consists of a programmable matrix of gates and multiplexers as shown in the logic diagram, Figure 2. The delay increment of the EP195B has a digitally selectable resolution of about 10 ps and a net range of up to 10.2 ns. The required delay is selected by the 10 data select inputs D9:0 values and controlled by the LEN pin 10. A LOW level on LEN allows a transparent LOAD mode of real time delay values by D9:0. A LOW to HIGH transition on LEN will LOCK and HOLD current values present against any subsequent changes in D10:0. The approximate delay values for varying tap numbers correlating to D0 LSB through D9 MSB are shown in Table 6 and Figure 3.

Features

---

|

- .

- Maximum Input Clock Frequency >1.2 GHz Typical

- .

- Programmable Range: 0 ns to 10 ns

- .

- Delay Range: 2.2 ns to 12.2 ns

- .

- 10 ps Increments

- .

- PECL Mode Operating Range:VCC = 3.0 V to 3.6 V with VEE = 0 V

- .

- NECL Mode Operating Range:VCC = 0 V with VEE = 3.0 V to 3.6 V

- .

- IN/INb Inputs Accept LVPECL, LVNECL, LVDS Levels

- .

- A Logic High on the EN Pin Will Force Q to Logic Low

- .

- D10:0 Can Select Either LVPECL, LVCMOS, or LVTTL Input Levels

- .

- VBB Output Reference Voltage

| 型号/品牌 | 代替类型 | 替代型号对比 |

|---|---|---|

MC100EP195BMNR4G ON Semiconductor 安森美 | 当前型号 | 当前型号 |

MC100EP195FAG 安森美 | 完全替代 | MC100EP195BMNR4G和MC100EP195FAG的区别 |

MC100EP195BFAG 安森美 | 完全替代 | MC100EP195BMNR4G和MC100EP195BFAG的区别 |

MC100EP196BMNG 安森美 | 完全替代 | MC100EP195BMNR4G和MC100EP196BMNG的区别 |