数字电路要运转稳固靠得住,电源一定要”清洁“,而且能量增补一定要实时,也便是滤波去耦必定要好。甚么是滤波去耦,简略的说就是在芯片不需要电流的时间存储能量,在需求电流的时间又能实时地增补能量。有读者看到这里会说,这个职责不是DC/DC、LDO的吗?对,在低频的时间它们能够搞定,但高速的数字体系就不同样了。

先来看看电容,电容的感化简略来讲便是存储电荷。咱们都晓得在电源中要加电容滤波,在每一个芯片的电源脚搁置一个0.1uF的电容去耦。然则,

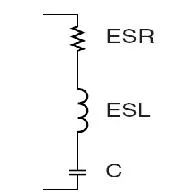

要搞懂这个道道就要懂得电容的实践特点。现实的电容它只是一个电荷的存储器,即C,而实践创造进去的电容却不是那末简略。阐发电源完整性的时间咱们经常使用的电容模子如图1所示。

图1

图1中,ESR是电容的串连等效电阻,ESL是电容的串连等效电感,C才是真正的现实电容。ESR和ESL是由电容的创造工艺和资料抉择的,无法排除。那这两个货色对电路有甚么影响?

电容的容抗

Zc=1/ωC

电感的感抗

Zl=ωL,ω=2πf

Z=ESR+jωL-1/jωC

=ESR+j2πf L-1/j2πf C

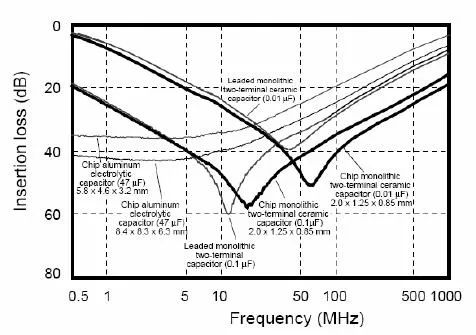

可见,再高时间电感就起主导作用了,电容落空滤波的作用了以是记着,高频时间电容就不是纯真的电容实践电容的滤波曲线如图2所示。

图2

陶瓷电容,ESL从零点几nH到几个nH不等,封装越小ESL就越小。

从图2中看出,电容的滤波曲线并非平整的,它像一个’V’,也就是说特点。有时候咱们但愿它越平越好(前级的板级滤波),而有时间但愿它越尖越好(滤波或陷波)。

影响这个特点的是电容质量要素Q:

Q=1/ωCESR

钽电容和铝电解有比较小的ESL,而ESR以是钽电容和铝电解拥有很宽无效频次局限异常适宜前级的板级滤波。也就是说,在DC/DC或许LDO输出经常使用较大容量的钽电容来滤波。而在接近芯片处所放一些10uF和0.1uF的电容往来来往耦,陶瓷电容有很低的ESR。

说了那么多,

|

| |

| DC-100K | 10uF以上的钽电容或铝电解 |

| 100K-10M | 100nF(0.1uF)陶瓷电容 |

| 10M~100M | 10nF(0.01uF)陶瓷电容 |

| >100M | 1nF(0.001uF)陶瓷电容、PCB电源与地间的电容 |