摘要

— 寄存器模数转换器的整体精度和线性度主要取决于其数模转换器 (DAC) 匹配特性。 随着 DAC 由于系统和随机失配的影响,分辨率的提高使得在地图上更难实现准确的电容比。 DAC 阵列的理想放置应尽量减少系统失配,然后随机失配。 本文提出了一种在内的布局策略 DAC 矩阵调整方法,。 由此产生的布局解决了系统性和随机性的不匹配问题。 我们考虑以下几点。 实验结果表明,与现有工作相比,布局策略实现了较小的电容比失配和较短的计算运行时间

【考虑的系统失配越来越多,那么有哪些呢? 【重点是二进制加权阵列】 为了应对二进制加权电容阵列中的所有列的布局策略,以应对这些挑战 该方法解决了系统性和随机性的失配,显著减少了计算运行时间。 考虑到以下系统性失配: 1)一步工艺梯度效应; 2)二阶光刻误差和邻近效应; 3) 布线的对称性和复杂性; 4) 远距离边缘场效应。

调研

连续接近寄存器 (SAR) 模数转换器 (ADC) 图是迄今为止最流行的数据采集应用架构 1 显示了传统 N 位 SAR ADC 架构示例。 一个采样保持器,一个比较器,一个 N 位电容数模转换器 (DAC) 阵列和一个 SAR 其中,控制逻辑组成 N 是 ADC 的分辨率。 至少比其他 ADC 架构好 10 而且经验证明 SAR ADC 最节能的分辨率的分辨率范围内 ADC [2],[3]。

四种ADC:SAR ADC优点是低功耗节能。

随着 DAC 分辨率的提高,在版图中实现准确的电容比变得更加困难,这会受到系统性和随机失配的影响。 系统失配是由环境不对称的同一设备引起的,随机失配是由加工条件或材料特性的统计波动引起的[4]和[5]。 氧化物 整体相关系数

启发式搜索方法旨在最大限度地分散布局,但布局可能没有共同的纹理布局,导致系统不匹配 [9]。 引入引入对称性、公共质心和一般放置的表示技术,但不会产生二进制加权电容阵列的最佳放置 [10]-[14]。 基于模拟退火 (SA-based) 该方法旨在提高分散度,最大限度地减少氧化物梯度失配,但由此产生的布局增加了布线的复杂性[15]和[16]

除了一级系统失配外,之前的研究还没有考虑到二级光刻误差、相邻效应、对称性和复杂性等二级加权电容阵列放置的以下系统失配 布线和远程边缘场效应。 例如,纳米 CMOS 在技术上,互连寄生电容器已达到飞法拉的数量级 DAC 单位电容器的电容已降至最先进 SAR ADC 几飞法拉的规模 [17] -[21]。 。 许多现有的方法除了放置约束外,还面临着计算。 例如,A32×32 矩阵中的 10 大约有位电容阵列 3×10604 种组合。 二进制加权电容阵列的组合数量阵列的组合数量 10 因此,在可接受的计算运行时间内更难实现优化目标。

一步工艺梯度效应通过矩阵调整最小化,为任何二进制加权电容阵列实现更对称的结构。电容阵列被虚拟单元电容包围,以减少二阶光刻误差和相邻效应。 其他虚拟电容器的放置采用空间加权法处理。 这种方法有助于最大化二进制加权 DAC 电容阵列的整体空间相关系数。 DAC单元电容器的放置采用对角加权法处理。 这种方法允许 DAC 同时保持对称和共质心的排列。这种布局类似于星形布局,因此与现有作品相比,增加了分散度,简化了布线的复杂性。 当单元电容器放置在不同的环境中时,电容器之间会有不同的远距离边缘场。 当先进 CMOS 在技术上,当单位电容器的物理尺寸和单位电容器之间的最小间距减小时,这种效大。 这种影响通过同质化最小化,解决了[23]中现有的权衡问题。实验结果表明,与现有工作相比,利用提出的放置策略获得的放置实现了氧化物梯度较小造成的失配和较短的计算运行时间。

在传统的 N 如图所示 2 所示,有 N 1 电容器,是的 b , b , 2 b , 2 1 b , . . . b,b,2b,2^1b,... b,b,2b,21b,...最常用的架构是实现N位电容阵列 C t y p e A C_{typeA} CtypeA和

为了与之前那些 [6]、[8]、[9]、[15] 和 [16] 等其他工作进行公平比较,本文采用了两种不匹配评估模型 [6]、[8 ]。 以下小节在 CtypeA 架构的上下文中回顾了这两个模型,并定义了模型的参数。

假设电容阵列在角度 θ 指定的方向上受到线性氧化物梯度 γ 的影响,如图 3 所示。由于氧化物梯度,位于不同位置的不同单元电容器经历不同的氧化物厚度,因此有效 任何单位电容器的电容为, 氧化物梯度引起的失配模型提供了对对称性和重合度的洞察,这对于纳米 CMOS 技术中的二进制加权电容阵列非常重要 [7]。 较小的电容失配比 M 在电容阵列中产生较小的系统失配。 为了与其他作品进行公平比较,我们假设氧化物厚度 t0 为 40 nm,氧化物梯度 γ 为百万分之十,单位电容器的宽度和长度 Cu 为 25 μm(W) x 25 μm( H) 间距分别为 9.1 μm(Sx)×2.6 μm(Sy),如图 3 所示。

我们的下一步是分别优先放置虚拟电容器和电容阵列。 这消除了二阶光刻误差和邻近效应,并最大限度地提高了电容阵列可以实现的色散度。 为了简化共质心布局中的布线,提出了,从而允许我们使用简单的矩形和对角线布线方法将电容器连接在一起。 最后,同质化算法应用于矩阵[23],这允许电容阵列之间更好的寄生电容分布。 如图 4 所示的流程图提供了我们提出的放置策略的详细信息。

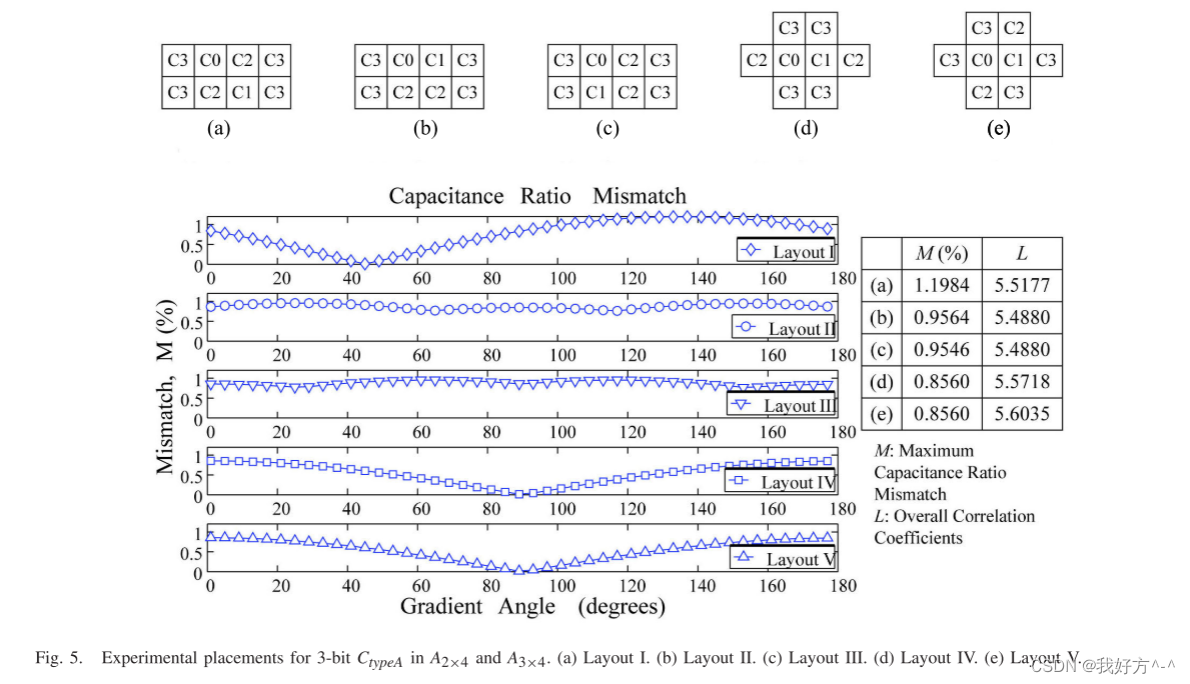

图 5 展示了 3 位 CtypeA 布局的五个不同示例,用于讨论我们的矩阵调整方法。 图 5(a)显示了 A2×4 中的布局(布局 I),其中 CA 0 和 CA 1 对角放置,关于原点部分对称。 图 5(b) 和 © 显示了 A2×4 中的布局(布局 II 和 III),分别关于 y 轴和 x 轴部分对称,其中 CA 0 和 CA 1 放置在相邻侧。 CA 0 和 CA 1 的这种相邻侧放置导致 M 和 L 减少,如图 5 中的表格所示。图 5(d)和(e)显示了 A3×4 中的布局(布局 IV 和 V),其中 分别关于 x 轴对称和关于原点的部分对称。 通过将矩阵改为 A3×4,M 和 L 都有进一步的改进。 其中氧化物引起的失配是遍历所有 θ \theta θ得到的最大失配值

如图 5 所示,电容比失配变化相对于这些布局的梯度角的曲线图为我们提供了有关布局对称特性的深刻细节。 基于本实验中研究的所有布局,进行了以下观察

- C t y p e A C_{typeA} CtypeA 在 C 0 A C_0^A C0A和 $C_1^A} 中包含一个奇数单位电容器,因此,很难在 A o d d × o d d A_{odd×odd} Aodd×odd 或 A e v e n × e v e n A_{even×even} Aeven×even 中实现最小 M。 A o d d × e v e n A_{odd×even} Aodd×even 或 A e v e n × o d d A_{even×odd} Aeven×odd 为 C t y p e A C_{typeA} CtypeA 电容阵列提供了更好的对称性。 C t y p e A C_{typeA} CtypeA应该选择 e v e n × o d d o r o d d × e v e n even × odd or odd × even even×oddorodd×even 其中$even × even $如果是方形也许还好?

- 奇数电容器的相邻边放置产生较小的M。因此,优选将 C 0 A C_0^A C0A和 C 1 A C_1^A C1A放置在相邻边并且它们应该放置在矩阵的中心附近。 【奇数电容器应该放在中间,并且临近靠近比原点对称好】

- 电容器对的对角线放置,从 C 2 C_2 C2 到 C N C_N CN,比相邻的侧面放置产生更高的 L。成对的电容器,对角放置比临近放置有更大的L。

- C t y p e A C_{typeA} CtypeA在具有对称失配变化时实现更好的对称性。

如图7 请注意,W0 和 ρ0 分别表示最短的 dl,w 和最高的 Ll,w。 比较距离加权法和空间加权法,后一种方法在不同类型的条目之间提供了更清晰的区分。 因此,空间加权方法用于虚拟单元电容器的放置。 虚拟单元电容器从最小的 Ll,w 开始分配,以便电容阵列能够在 AL×W 中实现最大 L。 用于 9 位 CtypeA 电容阵列的虚拟电容器的布局布局如图 8 所示。 使用空间加权方法放置虚拟电容器 在调整矩阵以实现最小 M 之后,下一个优先事项是虚拟单元电容器的放置。 尽管虚拟单元电容器不会引起失配,但它们的位置会影响电容阵列的匹配。 为了尽量减少这些失配,重要的是要考虑虚拟单元电容器的放置。 CD 基于矩阵大小和电容阵列计算。 这些虚拟单元电容器首先被添加到电容阵列的周边以充当相邻结构,从而最大限度地减少二阶光刻误差。 评估了两种加权方法以确定对 AL×W 中剩余虚拟单元电容器的位置进行优先级排序的最佳选择。

我们提出了一种电容阵列放置的对角加权方法。 在对角加权方法中,一对两个对角入口权重被定义为相对于 AL×W 的中心对角相对且等距。

数据集

实验指标

具体方法

我们提出了一种。 在对角加权方法中,一对两个对角入口权重被定义为相对于 A L × W A_{L×W} AL×W 的中心对角相对且等距。 此方法分为以下步骤。

1) C t y p e A C_{typeA} CtypeA中的第一对入口权重,记为 D 0 D_0 D0,是最靠近矩阵中心的前两个入口, A o d d × e v e n 。 图 9 ( a ) 说 明 了 第 一 对 入 口 权 重 , A_{odd×even}。 图9(a)说明了第一对入口权重, Aodd×even。图9(a)说明了第一对入口权重,D_0$in A 7 × 6 A_{7×6} A7×6。 2) 下一个入口对 D1 与前一对 D0 相距一个单位距离,从 12 点钟位置顺时针方向开始。 然后将 D2 与 D1 镜像放置在矩阵的中心附近。 3) 迭代地重复步骤 2,其中后续奇数对从 12 点钟位置按顺时针顺序放置,距离前一对奇数对角权重有 √2 个单位距离。 接下来的偶数项对被放置为与前一个奇数项对的镜像。 这个序列重复直到入口对到达虚拟单元电容器的边界。 图 9(b) 说明了 A7×6 中条目对 D1 到 D6 的位置。 请注意,放置的元素类似于字母 X 4) 下一对入口权重 D7 放置在相对于矩阵中心从 3 点钟位置顺时针方向最近的空入口处。 5) 下面的偶数对 D8 从距矩阵中心的 3 点钟位置单位距离顺时针放置,其中 i 从 1 递增, (kx, ky) 等价于 (0.5, 1 )。 6) 随后的偶数入场对 D10 相对于形成“X”右下角的对角线与 D8 对角放置。 然后所有后续的偶数入口对依次放置在这条对角线的上方和下方,直到它们到达虚拟单元电容器的边界。 7) 对应的奇数项对被放置在关于 y 轴的偶数项对的镜像中。 8) 重复步骤 4 到 7,直到步骤 4 到达虚拟单元电容器的边界。 9)使用距离加权方法[16]定义剩余的对角线入口权重。 图 7© 显示了一个用对角加权法对矩阵 A7×6 完成分配的例子。

CtypeB 的对角线权重方法与 CtypeA 相似,只是前两对入口权重 D0 和 D1 是从距离中心最近的 12 点钟和 3 点钟位置选择的。 矩阵 Aeven×even 和 (kx, ky) 等价于 (1.5, 0.5)。 电容器对序列是通过在 C 中迭代配对两个单位电容器形成的,从 C0 到 CN,由 [16] 修改而来。 类似地,从 D0 开始形成对角线对序列。 然后,将电容器对分配给相应的对角线对。 图 10 显示了 CtypeA 在 AL×W 中的位置。 我们提出的电容阵列放置方法确保 CN 中的单元电容器与其余单元电容器相邻放置,并允许 CN 均匀分布在整个矩阵中。 由于从 C2 到 CN-1 的大部分单位电容器都被 CN 包围,因此可以最大限度地减少电气失配。 我们假设从电容器对角线到单位电容器的远距离边缘效应可以忽略不计。 与 Hakkarainen 和 Nurminen 的方法 [23] 相比,所提出的方法不需要额外的虚拟电容器来改善电气匹配。 为了进一步改善与虚拟电容器相邻的单元电容器的电气失配,我们专注于优化这些单元电容器的放置, 任何具有有效单元电容器的条目 al,w 都分配有边缘权重,用 El,w 表示,其中 El,w 是与条目 al,w 相邻放置的虚拟单元电容器的总和。 令 Ec 表示属于电容阵列的一组边缘权重,其比率为 Ec,0 : Ec,1 : Ec,2 : … Ec,j : … : Ec,N,其中 Ec,j 是总和 在属于 Cj 的所有 El,w 中,让 E 表示一组边权重,其比率为 E0 : E1 : E2 :… Ej : …: EN,其中 Ej 定义为 Etotal 表示 AL×W 中所有边权重的总和。 Ej 提供了来自 Cj 的单元电容器的估计数量,该单元电容器需要放置在与虚拟单元电容器相邻的一侧。 目标是确保 Ej 和 Ej-1 之间的比率接近一个 3 位 CtypeB 电容阵列,它是通过将金属-绝缘体-金属 (MIM) 电容器与屏蔽层下方的布线连接而构建的。 如图12 每个电容器都被C9包围 图 12 显示了在 A27×26 中使用虚拟单元电容器的 9 位 CtypeA 的电容器放置示例。 虚拟单元电容器的放置策略性地使电容阵列的整体空间相关系数最大化。 布局类似于星形图案,从而最大化整体空间相关系数, 彩色矩形线和斜线代表电容器的布线。 布线方案表明,与 [8]、[22] 和 [16] 中介绍的布线方法相比,连接更加简单和对称。 将单位电容从 C 5 A C_5^A C5A 调整到 C 9 A C_9^A C9A 有助于在 C t y p e A C_{typeA} CtypeA 内的电容阵列边缘实现更均匀的边缘场分布。这有助于最大限度地减少由于不等边缘失配导致的失配。

【其中SA算法是当前的工作,比该办法相差较远,并且耗时要久非常多!该方法也可以作为一个对比方法,其真实电路性能未必比SA算法好,因为SA是存在一定折中的】

总之,重要的是在二进制加权电容阵列中实现零平均偏移或零系统失配,因为随机失配不能完全消除。 与最先进的作品相比,我们的分析方法显着改善了计算运行时间,同时实现了相当程度的分散性。

值得思考

- 论文考虑了四种系统失配,到底有多少种呢?

- [1]中最先进的 SAR ADC 的 Walden 品质因数 (FOM) 至少比其他 ADC 架构好 10 倍,并且经验证明 SAR ADC 在广泛的分辨率范围内最节能的 ADC [2]、[3]。这里应该指出的是SAR ADC和ADC其他架构的好处?是否可以借鉴呢?

- [5,22]布线方案的任何不对称。

- [23]单元电容器放置在不同的环境中时,电容器之间会发生不相等的远距离边缘场。 当先进 CMOS 技术中单位电容器的物理尺寸和单位电容器之间的最小间距减小时,这种效应会显着放大。 这种影响通过同质化方法最小化,该方法解决了[23]中现有的权衡问题。

- 需要详细看它的布局 因为表现比SA更好,运行时间更短。

- 为什么星型布线更简单??为什么考虑了这四种失配??

- C t y p e A C_{typeA} CtypeA[24][25]; C t y p e B C_{typeB} CtypeB [26][27]

- 同质化减少边缘寄生失配 [23]

- 存在两个问题:如何将步骤实现为算法?如何理解同质化算法? 怎么做改进?

Y. Li, Z. Zhang, D. Chua and Y. Lian, “Placement for Binary-Weighted Capacitive Array in SAR ADC Using Multiple Weighting Methods,” in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 33, no. 9, pp. 1277-1287, Sept. 2014, doi: 10.1109/TCAD.2014.2323217. [9]J.-E. Chen, P.-W. Luo and C.-L. Wey, “Placement optimization for yield improvement of switched-capacitor analog integrated circuits”, IEEE Trans. Computer-Aided Design Integr. Circuits Syst., vol. 29, no. 2, pp. 313-318, Feb. 2010. [10]L. Xiao and E. Young, “Analog placement with common centroid and 1-D symmetry constraints”, Proc. ACM/IEEE ASP-DAC, pp. 353-360, Jan. 2009. [14]P.-H. Lin, H. Zhang, M. Wong and Y.-W. Chang, “Thermal-driven analog placement considering device matching”, IEEE Trans. Computer-Aided Design Integr. Circuits Syst., vol. 30, no. 3, pp. 325-336, Mar. 2011. [15]C.-W. Lin, J.-M. Lin, Y.-C. Chiu, C.-P. Huang and S.-J. Chang, “Common-centroid capacitor placement considering systematic and random mismatches in analog integrated circuits”, Proc. IEEE/ACM DAC, pp. 528-533, Jun. 2011. [16]C.-W. Lin, J.-M. Lin, Y.-C. Chiu, C.-P. Huang and S.-J. Chang, “Mismatch-aware common-centroid placement for arbitrary-ratio capacitor arrays considering dummy capacitors”, IEEE Trans. Computer-Aided Design Integr. Circuits Syst., vol. 31, no. 12, pp. 1789-1802, Dec. 2012. [22]M.-H. Lin, Y.-T. He, V.-H. Hsiao, R.-G. Chang and S.-Y. Lee, “Common-centroid capacitor layout generation considering device matching and parasitic minimization”, IEEE Trans. Computer-Aided Design Integr. Circuits Syst., vol. 32, no. 7, pp. 991-1002, Jul. 2013. [23]“Layout of dummy and active cells forming capacitor array in integrated circuit”, Jan. 2003. [6]P.-W. Luo et al., “Impact of capacitance correlation on yield enhancement of mixed-signal/analog integrated circuits”, IEEE Trans. Computer-Aided Design Integr. Circuits Syst., vol. 27, no. 11, pp. 2097-2101, Nov. 2008. [7]A. Hastings, The Art of Analog Layout, Englewood Cliffs, NJ, USA:Prentice-Hall, 2006. [23]“Layout of dummy and active cells forming capacitor array in integrated circuit”, Jan. 2003.