电容器具有滤波功能,应该是每个硬件工程师最基本的知识。在某些芯片中IO嘴,我们可以看到0.1UF 100NF 4.7UF滤波电容的容值。

电容,一种小材料,其容值的选择在硬件电路设计和模拟中往往起着非常重要的作用。

工程师在进行电容滤波时,往往喜欢将电容分为旁路电容和去耦电容。翻了很多资料,大家都是根据位置来区分的,但在小白看来,其本质是一样的。也有人说,可以根据功能来区分,即去耦电容比旁路电容具有更多的储能功能。我觉得既然都是电容,为什么旁路电容不能储能,电容本身就有储能的作用,不局限于哪种电容。

众所周知,电容器在数字电路中起着储能和滤波的作用(为高频噪声电流提供低阻抗路径)。

本质上,在某种程度上,它几乎是完全统一的。您可以认为,电容器的储能为高频开关切换(芯片内晶体管来回切换)提供了瞬时电荷,以避免开关产生的高频噪声扩散到芯片的方向,因为开关切换所需的能量已经从芯片附近的电容器中获得。也可以认为旁路电容提供了高频噪声电流的低阻抗路径,避免了高频开关需要向更远的电源索取电荷能量。

虽说电容对滤波起到了很好的作用,但是在一些电路中,其容值的选取往往不好确定。芯片引脚位置放置0.1UF电容应该是我们最常见的。然而,一些板芯片放置在0.01UF,这到底有什么讲究?

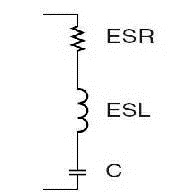

要理解这些,首先要了解电容器的特性。理想的电容器只是电容器的存储器,即C。实际制造的电容器并非如此简单。模型如下:

ESR是电容串联等效电阻,ESL是电容串联等效电感,C是理想的电容器。ESR与ESL由电容器的制造工艺和材料决定,不能消除。ESR通常影响电源的纹波,ESL影响电容器滤波频率。以下公式:

ESR是电容串联等效电阻,ESL是电容串联等效电感,C是理想的电容器。ESR与ESL由电容器的制造工艺和材料决定,不能消除。ESR通常影响电源的纹波,ESL影响电容器滤波频率。以下公式:

Zc=1/WC ZL=WL,W=2πf Z=ESR j(WL-1/wC)=ESR j(2πfL-1/2πfC) 从公式可以看出,当频率很低时,它的电容器就会工作。然而,当频率高到一定程度时,电感器的作用不容忽视。无论电感有多高,它都起着主导作用。由于电感通过直流电阻交流,电容器无法为高频噪声电流提供低阻抗路径。 理论上,随着频率的增加,理想电容增加而减少,但由于电容器两端引脚的电感效应,应视为一种LC串联谐振电路,自谐振频率为设备SFR参数表明频率大于SFR当频率超过时,电容变成电感。SFR对干扰的抑制将大大降低。

同时,容量越小,曲线向右偏移,SFR过滤频率越高。 通过这张照片,它还解释了为什么低容值可以过滤高频,高容值可以过滤低频。

说了这么多,靠近芯片的管脚放置多少电容器合适?以下是网上牛人列出的参考。 所以说,0.1UF不是万能的,只是在绝大多数场景中使用0.1UF。此外,从事手机行业的人也应该知道68pf滤波频率约为800M,33pF滤波频率9000左右M;15pF滤波频率约为1800M;

电容器有自谐振频率,也是数字电路的滤波电容器。UF原因大多是4.7UF。当然,容量不能太小,太小不能满足开关切换时瞬时所需的电荷。