CMOS 集成电路功耗(二)

CMOS 数字后端还必须掌握集成电路动态功耗的认知;我们来谈谈。

动态功耗 = Switching Power Internal Power

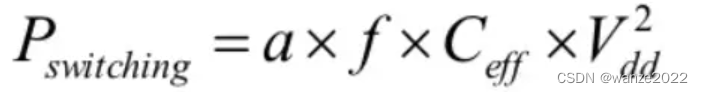

- Switching power 因为芯片 instance 上逻辑翻转充放电有效负载电容所消耗的功耗。公式如下:

其中,a 是 switching activity,它是电路节点从0跳转到1的概率(活动因子),或理解为整个电路的平均翻转率a,也是电路没有1/f 时间内产生的电平跳变(平均)次数。

这里栗子,a=25%;

f 是 clock frequency,Ceff 有效负载电容,Vdd 芯片电源电压;

以反相器为例,设置跳变功耗Vin 当输入端为f时,周期为f的方波Vin从高电平到低电平,P 管道逐渐打开,N管逐渐关闭,此时电源端Vdd给等效电容CL充电,Vout逐渐跳变为Vdd; 当Vin 从低电平到高电平,N管道逐渐打开,P管逐渐关闭,电容CL 开始向地端放电,这个过程被理解为跳变功耗。

2)Internal power 在输入从0到1或从1到0的瞬变过程中,NMOS管 和 PMOS管 短路电流同时消耗的功耗;又称短路电流功耗;

更低阈值电压或更低阈值电压 transition time 晶体管大(开关频率低) internal power 占动态功耗的主要部分;

有以下办法可以降低翻转功耗:

(1)使用clock gating 技术

减少活动因子是降低翻转功耗的方法之一,已经成熟易用;

(2) 减小毛刺Glitch

减少毛刺会减少活动因素,有助于降低功耗;

竞争和冒险是数字电路中的一种现象。

竞争: 在组合电路中,信号通过不同的方式到达某个汇合点。这种现象被称为竞争

冒险:由竞争引起的电路输出瞬时错误称为冒险。表现为原设计中没有的窄脉冲,通常称为毛刺。

有竞争不一定会产生毛刺,有毛刺一定会有竞争。

(3)减少等效负载电容

电容器来自电路中的连接instance负载。结合后端的实现,两者基本正相关,可以缩短相互连接的长度。当然,通过优化设计,减少逻辑门总数和相应面积,减少等效电容。

(4)降低系统电压

动态功耗与电压有平方关系,降低电源电压可显著降低功耗。

芯片分为多个电压域,每个电压域可以根据特定电路的需要进行优化。例如,该方法已广泛应用于存储器使用高电源电压来确保存储单元的稳定性power在敏感设计中,易于使用;低电压设计低速电路;

(5)动态电压调节DVS

CPU处理不同的任务有不同的性能要求。对于低性能要求的任务,可以使时钟频率降低到足以按预定时间完成任务的最低值,然后使电压降低到该频率下工作所需要的最小值就可以节省大量的能耗。

(6)降低频率

动态功耗与频率成正比。芯片只应在所需频率下工作,不应比所需频率快。降低频率还可以使用较低的电源电压,大大降低功耗。

(7)使用谐振电路

谐振电路通过在储能元件如电容器或电感器之间来回传输能量,而不是排放能量来降低转动功耗。

到了后端,后端的小伙伴们,可以关注一下这些是如何反映在后端相关设计中的;欢迎讨论。

请注意更多内容: