从0到1入门STM32最小系统板-绘制原理图的设备选择

我们这次选择的芯片是STM32F446RET6,使用立创EDA绘制原理图。

文章目录

- 从0到1入门STM32最小系统板-绘制原理图的设备选择

-

- 0.芯片

- 1.电源电路

-

- 1.1.电源芯片

- 1.2.去耦电容

- 2.晶振

-

- 2.1.晶振选型

- 2.2.电容计算

- 2.3.晶振原理图

- 3.下载电路

-

- 3.1.接线端子

- 3.2.SWD原理图

- 4.复位电路

-

- 4.1.简易复位电路

- 4.2.按键设计

- 5.检查

-

- 5.1.人工检查

-

- 5.1.1.VDD,VDDA

- 5.1.2.VSS

- 5.1.3.BOOT0,BOOT1

- 5.2.立创检查

-

- 5.2.1.警告

- 5.2.2.错误

- 6.注意事项

0.芯片

这篇文章不解释芯片的选择。先挖个坑,等一会儿再写个博客。

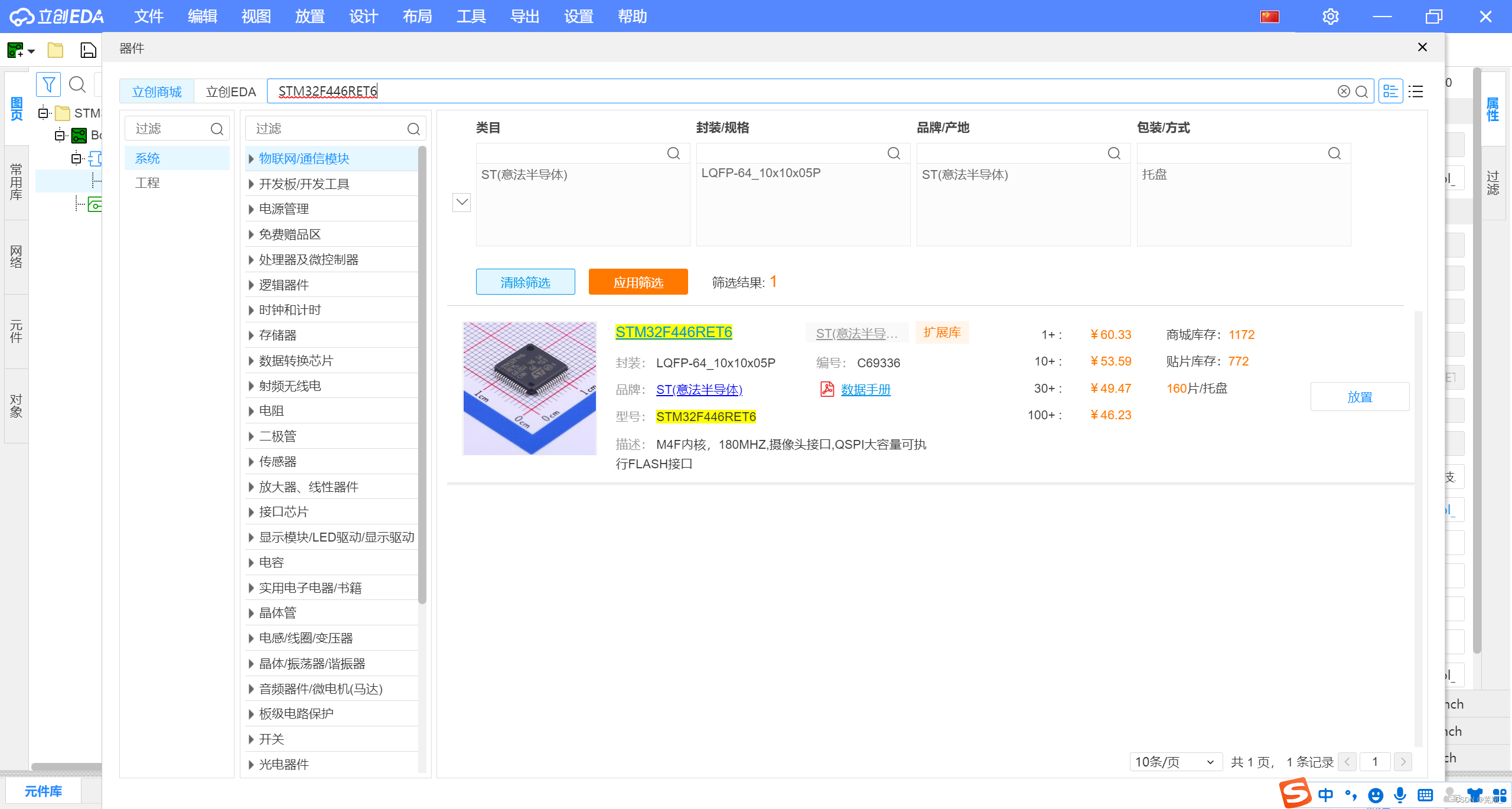

我在这里选择芯片STM32F446RET6。打开立创EDA,新建工程完成后,打开原理图。Shift F快捷键打开设备库,输入STM32F446RET搜索结果如下:

点击图片进入立创商城,下载其数据手册。数据手册必须保存并仔细查阅。作者的建议是单独放在文件夹中查看。EDA,点击放置,找到合适的位置,左键放置,右键取消放置。

我们修改其位数,并引出电源引脚、时钟引脚等。

1.电源电路

1.1.电源芯片

我们通常使用它USB接口直接向开发板供电,但是USB接口输入电压为5V,超过芯片电压3.3V,因此,为了使板正常工作,我们需要降低压力,通常使用LDO来实现这个功能。

LDO即low dropout regulator,是低压差线性稳压器。这与传统的线性稳压器相比。78XX输入电压至少比输出电压高2V~3V,否则不能正常工作。但在某些情况下,这种情况显然太苛刻了,比如5V转3.3V,输入输出之间的压差只有1.7v,显然,这不符合传统线性稳压器的工作条件。鉴于这种情况,芯片制造商开发了它LDO类电压转换芯片。(百度百科来源)

常用型号有AMS1117-3.3和LM1117-3.3.当然,您也可以选择其他更合适的芯片。我们在立创EDA中按Shift F快捷键打开设备库,输入LDO 3.搜索3,选择线性稳压器进行筛选(LDO)并应用筛选,如下图所示:

LDO一般没有特殊要求,只需注意最大输入电压即可。作者的初步选择是C347376这款,进入立创商城:

最大输入电压为8V,我们USB输入的是5V,足够了。下载其数据手册查看参考电路设计:

VIN和VOUT和地之间连接一个电容,C1的作用有2:

- 第一个功能是滤波,可以过滤VIN中的噪声;

- 第二个功能是可以让VIN电压缓慢上升,起到软启动的作用。VIN上电以后,C1会先充电,充电后VIN值变为5V;

C2的主要功能也可视为滤波。

回到立创EDA,单击鼠标左键放置,然后右键取消放置。这还没有结束。我们还需要根据数据手册中的基本电路再次放置两个电容器Shift F打开设备库搜索1uf 50v在筛选中选择贴片电容(MLCC),包装选择0603,品牌选择村田

第一个3美分,价格可以,只需查看参数即可使用,点击放置,将两个电容器放置在相应的位置,如下图所示:

选中LDO,翻转空间两次,然后先给它VIN接VCC,VOUT接 3.3V,VSS接地:

然后我们理图中连接两个电容:

注意将注释调整到合适的位置,并注意更改位号以便于阅读。

1.2.去耦电容

去耦电容器的意义主要是去除电源的噪声。如果你想更充分地了解去耦电容器,你可以移动B站老板圈的视频大小吗?位置不对?解耦电容器将如何影响电路工作_哔哩哔哩_bilibili。如何选择去耦电容的大小?

打开芯片数据手册,找到电特性Electrical characteristics一章可以找到供电方案Power supply scheme,如下所示:

可以看到VDD和地之间有几个1000nF和一个4.7uF电容连接:

具体多少个100nF这取决于我们有多少人VDD例如,我们现在有六个需要使用的人VDD,那我们就需要6个100nF的电容。我们按照上面同样的方法选择100nF筛选电容器,综合考虑价格、包装、精度、库存等因素C14663这个电容。然后作者选择了同样的方法C69335这个电容。**组件的选择没有固定,需要看自己的需!要看自己的需要!**这里作者只是为了方便一些没有自己选择组件的人,提供一个选择的想法!

我们把元器件放在原理图中,但是太乱了:

此时可使用EDA其布局功能使其等距分布,快捷键Ctrl Shift H,效果如下:

连接,放置位号:

这里需要注意的是模拟GNDA和数字地GNDD它是不同的,需要分开,两者可以通过0Ω电阻连接,这里作者选择C21189:

2.晶振

2.1.晶振选型

我们在这里选8MHz无源晶振,9倍频可达72MHz。我们搜索“8mhz作者最终选择筛选无源晶振C403948,大家可以自己选择。

2.2.电容计算

打开数据手册,需要找到其负载电容:

即12pF。

这里需要补充一个公式: C f = C d ? C g C d C g C i c Δ C C_f=\frac{C_d*C_g}{C_d C_g} C_ic \Delta C C

2.3.晶振原理图

放置电容,筛选两个18pF的电容,笔者选择的是C107040,放置两个后进行原理图绘制,如下所示:

3.下载电路

STM32的下载有多种方式,为了节省空间,我们选择SWD下载模式,该模式只需要4根线,分别为SWDIO、SWCLK、GND和3.3V。有关下载的部分在这里挖个坑,以后要是发了文章再回来填上这个坑,这里就不再讲了。

3.1.接线端子

我们需要选择一个4pin的接线端子,用于连接ST-Link。我们搜索“4pin”,筛选选择“线对板/线对线连接器”和“插件,P=2.54mm”,如下所示:

然后按自己的需求进行挑选即可,我选择的是C2905435,大概长这个样子:

3.2.SWD原理图

放置到合适的位置,然后四根线分别接GND、3.3V、SWDIO和SWCLK,接好后如下图所示:

但是问题来了,在芯片中,并没有标注SWDIO和SWCLK:

所以我们还需要去芯片数据手册中查找到底要接在哪个IO口上。搜索SWDIO,很轻松找到了相应的IO口:

我们在原理图上标注好引脚的网络号:

4.复位电路

复位电路相对简单,可以选择有按键复位也可以选择无按键复位。我们这里设计一个有按键复位的电路。

4.1.简易复位电路

我们首先先将基础的复位电路画好。基础的复位电路需要一个电阻和一个电容,组成一个RC电路,电容起到一个软启动的作用,在上电之后,电容先进行充电,缓慢达到3.3V。当电容的充电时间大于芯片复位所要求的时间时,就可以完成复位。这里采用的电阻是10K,选项为C25804,电容是0.1uF,与之前用的相同。电路设计如下:

4.2.按键设计

如何通过按下按键实现复位呢?按下按键以后RST变为低电平,松开按键以后给重新进行电容充电实现软启动,从而进行复位。因此,我们的按键应该接在RST和GND中间。按键选型没有太多要求,笔者搜索的是“按键”,筛选类目选择“轻触开关”,封装/规格选择“SMD”。最终选择了C83206这一款按键,原理图更改如下:

5.检查

5.1.人工检查

5.1.1.VDD,VDDA

我们发现在绘制的时候还没有将+3.3V,VDD,VDDA统一,补充如下:

由于我们不使用备用电源,VBAT也要接到VDD上:

5.1.2.VSS

在芯片中没有将VSS标明,进行补充如下:

5.1.3.BOOT0,BOOT1

发现还没有设置BOOT0和BOOT1为0,但是芯片中并没有直接标明BOOT1,只标注了BOOT0,我们打开手册搜索一下BOOT1即可:

将BOOT1从芯片中引出:

我们将两个引脚下拉:

下拉的原因是为了设置单片机的启动模式,如下表所示:

一些单片机是通过跳线帽来选择启动方式,我们为了简洁,就不再设置跳线帽了,直接都置0。

5.2.立创检查

点击设计,点击检查DRC:

为了便于观察,我们首先清空,然后再次检测DRC:

5.2.1.警告

先查看警告:

意思说一串引脚悬空,这是指芯片上没有用到的引脚,我们把它们都打叉,示例如下:

所有没有用到的引脚都这样操作即可,所有引脚都打叉后清空记录,重新进行检查:

警告已经全部修改结束了。

5.2.2.错误

两个错误都是在这一部分,这一部分我在立创社区电子工程师交流社区_电子发烧友论坛_嘉立创&立创商城旗下专业电子论坛【立创社区】 (szlcsc.com)搜索到了两种解决办法,原贴原理图中经常需要将两个PowerPort短接,专业版短接后会报错 - 立创社区 (szlcsc.com)。

:修改设计规则。在设计中打开设计规则:

将特殊符号含有“全局网络名”属性时,所连导线的名称需要与“全局网络名”的值一致这一项取消检查即可。

设置好后清空日志,重新检查一下,已经没有错误了:

:不使用特殊符号,使用导线添加网络名,如下所示:

这样也可以达到效果,无错误:

个人觉得方法二还是更合适一些,不用修改设计规则,而且也同样非常明晰。

6.注意事项

- 遇到问题可以从立创论坛上电子工程师交流社区_电子发烧友论坛_嘉立创&立创商城旗下专业电子论坛【立创社区】 (szlcsc.com)搜索答案,作为新手第一次使用立创EDA进行画图还是难免会有很多奇奇怪怪的问题,论坛上说不定就有其他人也有过类似的问题。比如笔者在做这个原理图时就是通过论坛才搜到了错误的解决办法;

- 如果问题没有搜到结果,可以询问立创的技术支持,注册账号绑定微信后应该会有技术人员加好友的;

- 保存好数据手册,手册占不了特别多的空间,主要是便于查阅;

- 到这里最小系统板的原理图已经绘制完成了,但是还需要进行原理图布局,使得别人在阅读原理图时更加方便。笔者计划在下一篇中再加几个其他的设计,所有设计都完成后再进行布局。