本章目录

- 一、CMOS器件

-

- 1.1CMOS 反相器

- 1.2 CMOS 与非门(NAND)

- 1.3 CMOS或非门(NOR )

- 1.4CMOS与门和CMOS或门

- 1.5 CMOS重要的电路技术参数

- 二、CMOS功耗及解决方案

-

- 2.1 时钟门控(clock gating)

- 2.2 动态电压频率调整DVFS

- 2.3.多阈值电压技术

- 2.4.多电源多电压技术技术

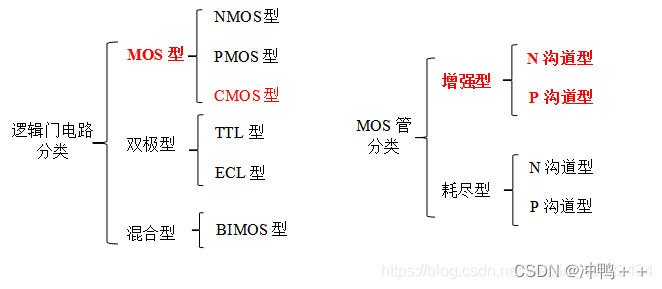

一、CMOS器件

1.1CMOS 反相器

CMOS由反相器实现非门功能PMOS管和一个NMOS逻辑电路图如下:

| In | PMOS | NMOS | OUT |

|---|---|---|---|

| 0 | 导通 | 关闭 | 1 |

| 1 | 关闭 | 导通 | 0 |

在实际制造过程中,PMOS管比NMOS因为管要宽PMOS管道由空穴导电,NMOS由于电子导电,电子迁移率远高于空穴迁移率(约2倍)。

1.2 CMOS 与非门(NAND)

CMOS与非门并联PMOS管,两个串联NMOS管组成的。

| A | B | PMOS (A) | PMOS(B) | NMOS(A) | NMOS(B) | OUT |

|---|---|---|---|---|---|---|

| 0 | 0 | 导通 | 导通 | 关闭 | 关闭 | 1 |

| 0 | 1 | 导通 | 关闭 | 关闭 | 导通 | 1 |

| 1 | 0 | 关闭 | 导通 | 导通 | 关闭 | 1 |

| 1 | 1 | 关闭 | 关闭 | 导通 | 导通 | 0 |

1.3 CMOS或非门(NOR )

CMOS或者个串联的非门PMOS管,两个并联NMOS管组成的。

1.4CMOS与门和CMOS或门

分别将CMOS与非门、CMOS或非门的VDD端与接地端可以交换,可以通过真值表验证,这里不再给出具体的CMOS电路图。

1.5 CMOS重要的电路技术参数

1.输入输出的高低电平; ??输入低电平的上限值VIL(max) ??输入高电平的下限值VIH(mix) ??输出低电平的上限值VOL(max) ??输出高电平的下限值VOH(mix) 2.噪声容量-门电路的抗干扰能力,电路的噪声容量越大,抗干扰能力越强。 ??输入高电平噪声容限:VNH = VOH(mix) - VIH(mix)(输出-输入) ??输入低电平噪声容限:VNL = VIL(max) - VOL(max)(输入-输出) 3.传输延迟时间表示门电路开关速度的参数,其值和电源电压VDD与负载电容有关。 3.功耗-分为静态功耗和动态功耗。 4.延迟-功耗积-测量电路综合性能指标(工作速度快,功耗低) 5.扇入和扇出数-表示门电路的输入端信号数和输出端信号数。

二、CMOS功耗及解决方案

CMOS电路功耗需要考虑两部分:静态功耗和动态功耗;静态功耗是指电路输出无动态转换时的功耗。动态功耗是指电路状态转换时的功耗。动态功耗主要包括两部分:一是指电路输出状态转换时的功耗MOS管的导通功耗,二是指电路输出由高电平转为低电平,或从低电平到高电平(CMOS充放电过程中管道负载为电容性),增加电路损耗。

动态功耗由开关功耗(翻转功耗)和短路功耗组成。

总功耗 = 静态功耗 开关功耗 短路功耗

翻转功耗 = Cv^2F ??C 负载电容,V是电压,F是频率 短路功耗 = V I(短路) ??I(短路)N极和P极在切换过程中同时有效短路电流 静态功耗 = V I(漏电) ??静态功耗(又称漏电功耗)是晶体管在电路稳定时漏电引起的功耗。

需要注意的是,提高电压可以提高电路性能,但也会增加功耗;温度升高也会增加功耗。如何有效降低电路设计中的功耗?主要是指动态功耗

可通过做),降低转速,即降低频率,降低电路功耗;此外,还可以降低电压,如

2.1 时钟门控(clock gating)

:当数据无效时,将能有效降低功耗的技术, 它是低功耗设计的重要方法之一。门控时钟实际上是一个逻辑模块, 当寄存器输入数据无效时,将寄存器输入时钟放置为0,此时寄存器值保持不变,此时无时钟翻转,避免动态功耗。

2.2 调整动态电压频率DVFS

(Dynamic Voltage and Frequency Scaling)动态电压频率调节本质上是一种自适应的电压频率调节技术,也是一种低功耗技术。目的是根据芯片当时的实际功耗需要设置工作电压和时钟频率,以确保提供的功率既满足要求,又不过度性能,从而降低功耗。 ??一味的降频降压当然是不能降低功耗的,因为低频下运行可能使系统处理任务的时长增加,从而整体上可能增加了功耗。所以DVFS其核心是动态调整策略,其目的是根据当时的系统负进行实时调整,从而提供满足当时性能要求的最低功耗。当然,基本策略是在工作负荷增加时先升压再升频,工作负荷降低时先降频。 ??例如,该技术可以动态调节CPU工作频率和工作电压,如CPU高速工作时,选择适当的电压供应CPU;当CPU在空闲或睡眠状态下,系统会自动切换到适当的低以降低系统功耗。

2.3.多阈值电压技术

该装置的格栅电压定义为阈值电压,即MOSFET其中一个重要参数。由于阈值电压不同Vth相应设备的漏电流Leakage差异很大,漏电流随阈值电压而变化Vt指数下降,

采用不同阈值电压的标准单元在不同时序路径上降低漏电流,达到降低漏电功耗的目的。

2.4.多电源多电压技术

**(MSMV)**它是一种能有效降低动态功耗的技术,简称多电压技术。所谓多电源,是指不同逻辑模块在不同的电源域由不同的电源供电。 ??具体来说,在芯片设计中,工作频率要求高的系统或模块使用高压,工作频率要求低的系统或模块使用相应的低压Normal从而达到低功耗的目的。 ??例如,在手机基带芯片中CPU或者GPU系统模块只下,系统模块才能满足系统的工作要求。对于一般只需要达到一般性能的模块,可以提供较低的电压,如系统需要一直上电Always-ON域中的Timer计时器等等。