数字IC设计笔试题汇总(3)

这个博客记录了最近看到的一些数字IC仅供参考

1,verilog代码覆盖率有哪些?这些覆盖率的意义是什么?

- (1). 语句覆盖率(声明覆盖率,statement coverage),每个声明(赋值语句)在模拟过程中被执行多少次,如果有声明没有执行,则需要模拟补充;

- (2). 路径覆盖率(path coverage),主要是以if - else句子是分析对象,用于分析哪些分支没有执行;

- (3). 状态机覆盖率(state machine coverage),统计状态机跳转情况,防止未跳转路径;

- (4). 触发覆盖率(triggering coverage), 比如always@(a ,b ,c),这个覆盖率用来表示电路是否是由a,b与c触发,如果模拟过程中没有被a触发,会给出提示;

- (5).表达式覆盖率(expression coverage),用来表示布尔表达式验证的充分性,如 assign c = a || b, 应出现的组合如下所示,表达式覆盖率用于表示下列组合是否出现在模拟过程中;

| a | b |

|---|---|

| 0 | 0 |

| 0 | 1 |

| 1 | 0 |

| 1 | 1 |

2,请写出switching power公式;请从前端设计的角度列出至少三种降低动态功耗的方法;请从门级电路的角度列出至少两种降低功耗的方法;

数字IC的功耗 P = P d y n a m i c P s t a t i c P = P_{dynamic} P_{static} P=Pdynamic Pstatic 其中,动态功耗 P d y n a m i c = P s w i t c h i n g P i n t e r n a l P_{dynamic} = P_{switching} P_{internal} Pdynamic=Pswitching+Pinternal,动态功耗由翻转功耗和内部功耗组成; 翻转功耗 P s w i t c h i n g = C e f f ∗ V d d 2 ∗ f c l o c k P_{switching} = C_{eff}* V_{dd}^{2} * f_{clock} Pswitching=Ceff∗Vdd2∗fclock,翻转功耗是信号翻转产生的功耗,由时钟频率、关断时的负载电容以及电压的平方决定。 内部功耗 P i n t e r n a l = t s c ∗ V d d ∗ I p e a k ∗ f c l o c k P_{internal} = t_{sc} * V_{dd} * I_{peak} * f_{clock} Pinternal=tsc∗Vdd∗Ipeak∗fclock, 内部功耗是指CMOS管翻转过程中,PMOS和NMOS同时导通产生的电流产生的功耗, 和晶体管输入发生翻转,但是输出来改变,但此时输入信号翻转仍会导致内部产生功耗。其中 t s c t_{sc} tsc指的是NMOS/PMOS 短路的时间。 I p e a k I_{peak} Ipeak指的是整个短路电流和导通电流的总和,

静态功耗 P s t a t i c P_{static} Pstatic也就是漏电功 P l e a k = V d d ∗ u ∗ C o x ∗ V t h 2 ∗ W L ∗ e V g s − V t h n V t h P_{leak} = V_{dd} * u *C_{ox} * V_{th}^{2}*\frac{W}{L} * e^{\frac{V_{gs} - V_{th}}{nV_{th}}} Pleak=Vdd∗u∗Cox∗Vth2∗LW∗enVthVgs−Vth, 这里的 V t h V_{th} Vth, C o x C_{ox} Cox , W / L W/L W/L都是工艺相关,不可以调整, V g s V_{gs} Vgs就是 V d d V_{dd} Vdd, V t h V_{th} Vth指的是阈值电压;

3,数字芯片的功耗包括(ABC) 详见问题2的回答

A. internal power

B. leakage power

C. swtiching power

D. random power

4,以下能减小静态功耗的是(B)?详见问题2的回答

A. 时钟门控

B. 电源关断

C. 降频

D. 采用低阈值电压的标准单元

5,以下哪项不是芯片signoff的检查步骤?(BC)

A. IR Drop

B. Synthesis

C. STA

D. PV

Signoff指将设计数据交给芯片制造厂商生产之前,对设计数据进行复检,确认设计数据达到交付标准。 IR Drop: 随着制成工艺的不断升级,金属连线的宽度越来越窄,致使电阻值越来越高。如果一个器件离供电点很远,其等效阻值必然会比较大,从而导致供电电压越来越小,这种现象就是IR Drop; STA: Static Timing Analysis(STA) 静态时序分析,是芯片设计中的一个后端流程,通常对设计的电路的时序路径进行分析。signoff的时序检查和STA互补,能检查到一些STA没检查到的路径; PV:关注芯片是否满足工艺设计规则,物理设计与逻辑网表的一致性 Synthesis:综合,将硬件代码影射为逻辑电路的过程,属于前端,signoff属于后端;

6,如下哪些指标是描述时钟特性的(ABCD)?

A. Period

B. Duty cycle

C. Frequency

D. Jitter

时钟特性有时钟周期(clock period)、时钟占空比(clock duty cycle)、时钟转换时间(clock transition time)、时钟延迟(clock latency)、时钟偏斜(clock skew)、时钟抖动(clock jetter)。

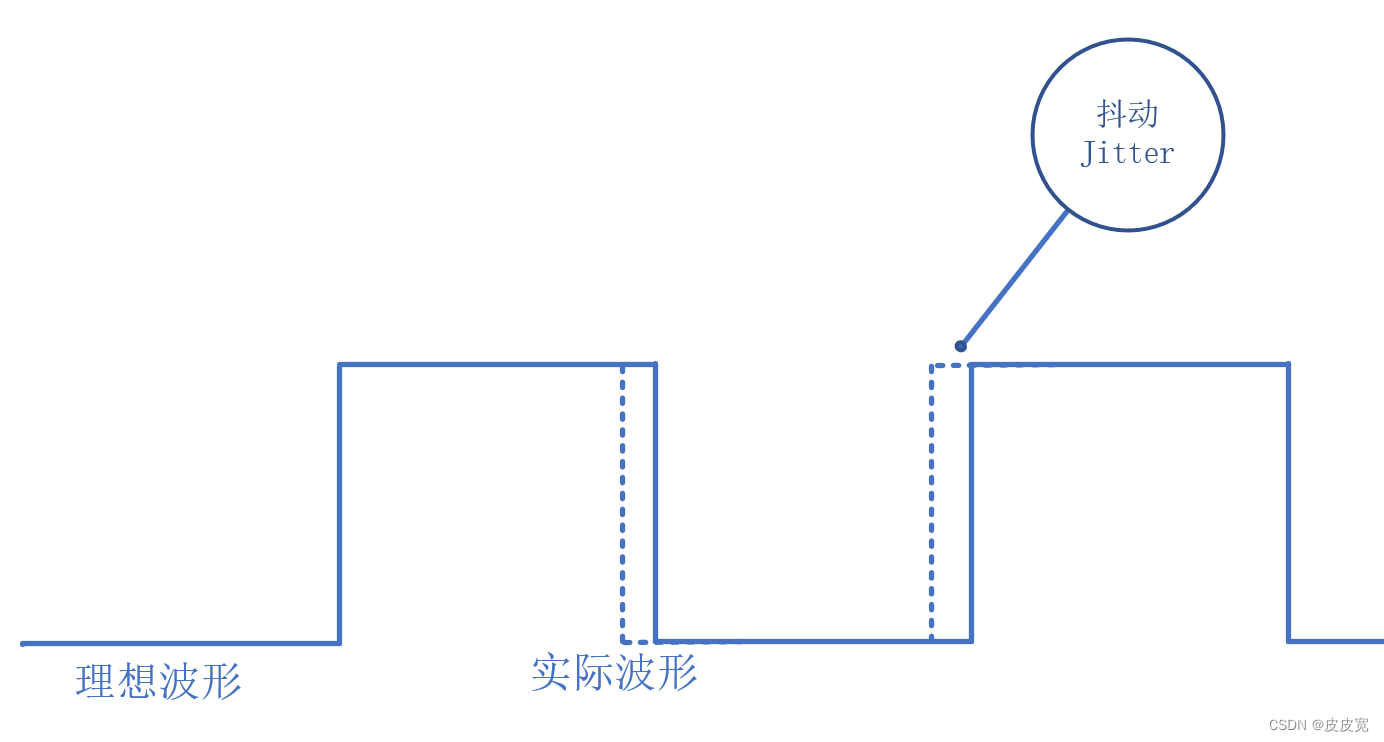

Jitter : 被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

时钟偏斜Skew:非理想情况下,由于时钟线长度以及时钟树叶节点负载不同等因素,导致时钟信号到达同一时序路径下的相邻两个时序单元的时钟端口的时间并不相同,这种时钟信号之间的偏移就是相同时钟信号之间的时钟偏斜。

时钟偏斜Skew:非理想情况下,由于时钟线长度以及时钟树叶节点负载不同等因素,导致时钟信号到达同一时序路径下的相邻两个时序单元的时钟端口的时间并不相同,这种时钟信号之间的偏移就是相同时钟信号之间的时钟偏斜。

7,logic synthesis的主要步骤是?

综合前:

-

(1)对代码进行语法检查

-

(2)功能仿真和验证

logic synthesis(综合)的主要步骤【12】:

-

(1)翻译:读入电路的RTL级描述,并将语言描述翻译成相应的功能块以及功能块之间的拓扑结构。

-

(2) 优化:根据所施加的时序和面积约束,按照一定的算法对翻译结果进行逻辑重组和优化。

-

(3) 映射:根据所施加的时序和面积约束,

综合后:

-

(1)形式验证(Formality):形式验证是一个系统性的过程,将使用数学推理来验证设计意图(指标)在实现(RTL)中是否得以贯彻。形式验证可以克服所有3种仿真挑战,由于形式验证能够从算法上穷尽检查所有随时间可能变化的输进值【10】

-

(2)静态时序分析STA

-

(3)仿真与验证

参考资料

【1】CSDN:Verilog代码验证的全面性与代码覆盖率分析 【2】CSDN:芯片功耗分析 【3】CSDN:IC设计中节省静态功耗和动态功耗的方法 【4】CSND:浅论芯片低功耗的设计实现(上) 【5】CSND:后端signoff含义 【6】CSDN:STA(静态时序分析)和LEC(逻辑一致性检查),为什么还要进行后仿真 【7】简书:IR drop 产生原理及危害 【8】CSDN:时钟抖动(Jitter)的基本概念 【转载】 【9】时钟特性 【10】百度百科:形式验证 【11】逻辑综合工具DC及操作流程 【12】CSDN :逻辑综合