硬件基础知识

- 1 引脚定义

- 2 PCB制作

-

- 2.1 原理图编译

- 2.1 导入设计数据

- 2 PCB设计

- 3 EMI

- 计算三部分原理

-

- 3.1分压原理

- 3.2 基尔霍夫原理

- 4 电路

-

- 4.1 LC谐振

- 4.2 基础滤波器

1 引脚定义

:电源输入端 :电源输出端 :芯片供电引脚,电源端,Vcc是双极器件的正,Vdd大部分是单极器件的正。下标可以理解为NPN晶体管的集电极C,和PMOS or NMOS现场效应管的漏极D。对数字电路而言,VCC是电路的电压,VDD是芯片的工作电压(通常Vcc>Vdd),VSS是接地点。有些IC既有VDD引脚又有VCC引脚表明该装置本身具有电压转换功能Vdd仅仅是给器件内部的数字或模拟系统供电,而Vcc供电包括外设和内部系统。 :接地 :负电压供电;场效应管的源极(S) : Feedback ,反馈 :参考电压,NP标识 和-

:Chip Select片选信号 :时钟使能 :片上终端电阻 :英文全称为Output Enable,中文是指输出使能端,输出允许信号。OE一个相应的电平值时,即一个高电平或者是低电平,要看芯片的要求,一般是高电平,使其选通,就允许芯片输出数据;否则,不能输出数据。 :过流保护 :复位 :行地址 :列地址 :写使能信号

:General-purpose input/output,引脚图中的常规输入输出 PA、PB、PC、PD 等均属于 GPIO 引脚。这么多GPIO管脚,可查阅STM32芯片数据手册获取具体引脚功能信息。 :数据信号 :Data strobe 数据选通 输出带读数据,输入带写数据。 对齐读取数据的边缘,以写入数据为中心。 :Data mask 数据掩码 写访问时,当DM采样到与输入数据一致的高电平时,屏蔽输入数据。 :Error-Correcting Code memory 纠正错误的存储器 :地址信号 :数据信号 :空 :Power-Down; 0 = Normal, 1 = Power-Down

补充 :STM32F4 datasheet中Power supply schemes 章节电源内部Block,可以看到VCAP_1和VCAP_2是VOLTAGE REGULATOR(调压器)相关的两个引脚,外接一个电容再接地。 **UART:**嵌入式串口。 :OSC_IN和OSC_OUT默认情况下晶振引脚。如果不使用若使用内部RC不使用外部晶振器的振荡器,请按以下方法处理: 1)100脚或144脚的产品,OSC_IN应接地,OSC_OUT应悬空。 2)对于少于100脚的产品,有两种接法: 2.1)OSC_IN和OSC_OUT分别通过10K电阻接地。这种方法可以改进EMC性能。 2.2)分别重映射OSC_IN和OSC_OUT至PD0和PD1,再配置PD0和PD1.推挽输出和输出0。这种方法可以降低功耗(与上述2相比).1)节省2个外部电阻。 :是同步输出的时钟,可以使用UART当成SPI用。 :蜂鸣器引脚 :数模转换引脚 :(Inter-Integrated Circuit)总线是一种由PHILIPS公司于20世纪80年代开发的两线串行总线用于连接微控制器及其外围设备。它是半双工通信。 从输入输出,主输入从输出:一般直接连接 信号 MISO = Master In Slave Out,即 输入在主机一侧,输出在从机一侧。

信号 MOSI = Master Out Slave In,即 主机侧输出,从机侧输入。

根据输入接输出和输出接输入的原理,应该是

SPI主机的 MISO,直接 接 SPI从机的MISO,因为前者是输入,后者是输出。 SPI主机的 MOSI,直接 接 SPI从机的MOSI,因为前者是输出,后者是输入。 也就是主机MISO需要接从机的MISO,主机的MOSI需要接从机的MOSI,不能交叉连接。 :天线接口。 是Chip Enable缩写是选择发射/接收状态的引脚。 片选择引脚. 可以中断引脚RFID当标签进入附近时,向微控制器发出警报。 MISO / SCL / Tx 当使能SPI接口时,引脚作为主从从从输出;当使能时I2C接口时,引脚作为串行时钟;当使能时UART接口时,该引脚充当串行数据输出。 MOSI (主输出从站输入)SPI 输入到RC522模块引脚。 是IIC(I2C)串行时钟引脚总线。 I2C串行总线一般有两条信号线,一条是双向数据线SDA,另一个是时钟线SCL。 所有接到I2C总线设备上的串行数据SDA都接到总线SDA上,每台设备的时钟线SCL接到总线的SCL上。 引脚:参考电流引脚

2 PCB制作

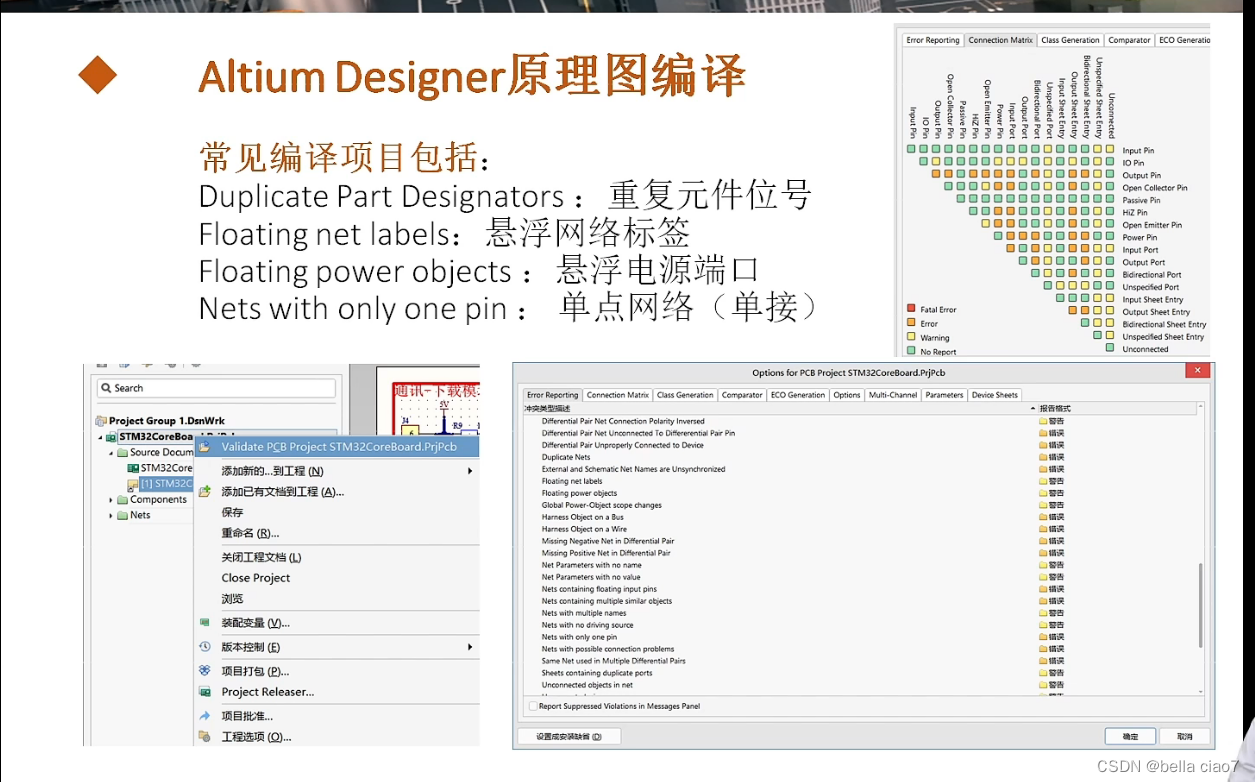

2.1 原理图编译

1.将常见项目列为致命危险  2.处理错误 遇到错误: 没有接线,单端网络可以忽略

2.处理错误 遇到错误: 没有接线,单端网络可以忽略

2.1 导入设计数据

1.检查封装管理器

2 PCB设计

https://blog.csdn.net/chenhuanqiangnihao/article/details/113941995 https://blog.csdn.net/Britripe/article/details/83899914

3 EMI

:电磁干扰指电子产品工作会对周边的其他电子产品造成干扰,与此关联的还有EMC规范。

辐射型EMI必须转换为传导型EMI才可以对PCB产生影响, 辐射型EMI传输是过介质以电磁波的形式传播,干扰能按照电磁场的规律传输到周围空间,然后产生干扰。类型可分为近端场效应和射频场效应,

3部分原理计算

3.1分压原理

3.2 基尔霍夫原理

4 电路

4.1 LC谐振

LC谐振,在含有电容和电感的电路中,如果电容和电感串联,可能出现在某个很小的时间段内: 电容的电压逐渐升高,而电流却逐渐减少;与此同时电感的电流逐渐增加,电感的电压却逐渐降低。 而在另一个很小的时间段内:电容的电压逐渐降低,而电流却逐渐增加;与此同时电流缺逐渐减少,电感的电压逐渐升高。 电压的增加可以达到一个正的最大值,电压的降低也可达到一个负的最大值,同样的电流的方向在这个过程中也会发生正负方向的变化,此时我们称为电路发生电的震荡

4.2 基础滤波器

滤波器是由电容电感电阻组成的滤波电路。滤波器可以对电源线中特定频率的频点