目录

- 1. 功能描述

- 2. 架构

-

- 2.1. axi_bus_matrix_4x4

- 2.2. decoder

- 2.3. axi_round_robin_arbiter

- 3. 逻辑设计

- 4. 测试

-

- 4.1. axi_round_robin_arbiter

-

- solo测试

- 3v1写测试

- 3v1读测试

- 4.2. axi_bus_matrix_4x4

-

- 4v1写测试

- 4v4写测试

1. 功能描述

当多个AXI master与多个AXI slave通信时,可以使用一个基于AHB协议的bus matrix实现互联。

例如

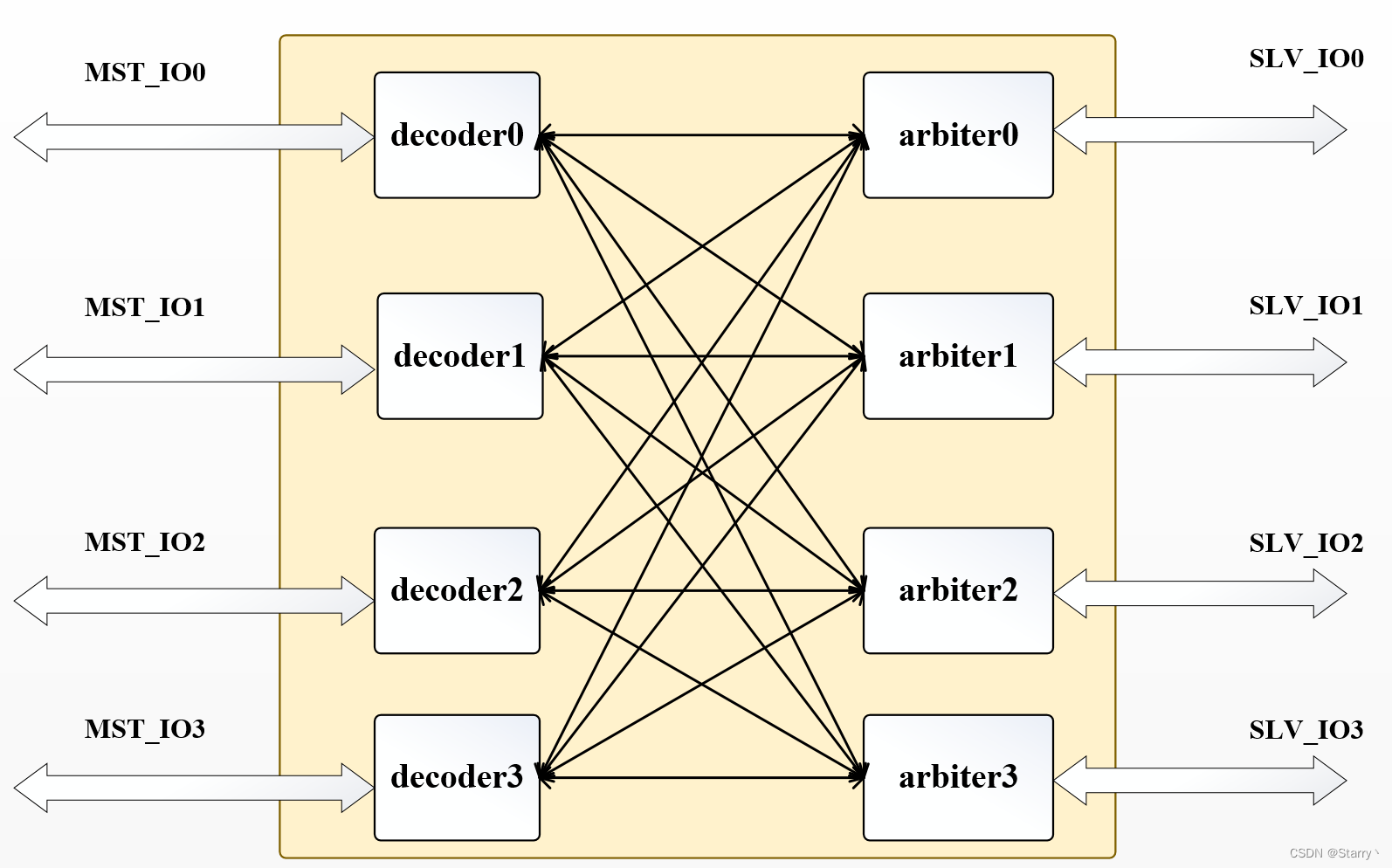

2. 架构

对于AXI来说,多个AXI Master需要多个AXI Slave通信,可以通过一个BUS MATRIX实现互联,架构如下图所示

可见AXI_Bus_Matrix与AHB_Bus_Matrix结构相似,都需要decoder解码以判断Master要与哪个Slave通信,回传R通道读数据和B通道写响应。

同时还需要arbiter,面对多个Master同时访问同一个Slave仲裁器。

2.1. axi_bus_matrix_4x4

接口如下

| Group | Channel | Signal | Direction | Width(bits) | Description |

|---|---|---|---|---|---|

| ACLK | input | 1 | 时钟 | ||

| ARSTn | input | 1 | 低效复位 | ||

| MST_IOx | AW | AWID_mstx | input | AWID_WIDTH | AW通道ID宽度 |

| AWADDR_mstx | input | AWADDR_WIDTH 2 | burst第一个写事务WDATA的地址,高2bit是为了片选axi slave | ||

| AWLEN_mstx | input | 8 | 该数值 1.意思是这次写事务。WDATA个数 | ||

| AWSIZE_mstx | input | 3 | WDATA中有效byte大小 | ||

| AWBURST_mstx | input | 2 | burst传输类型 | ||

| AWVALID_mstx | input | 1 | AW所有控制信息都是有效的 | ||

| AWREADY_mstx | output | 1 | AW准备接收所有控制信息 | ||

| W | WDATA_mstx | input | WDATA_WIDTH | 写数据 | |

| WLAST_mstx | input | 1 | 最后一个写数据的事务 | ||

| WVALID_mstx | input | 1 | W所有数据信息通道都有效有效 | ||

| WREADY_mstx | output | 1 | W准备接收通道所有数据信息 | ||

| AR | ARID_mstx | input | ARID_WIDTH | 读事务ID | |

| ARADDR_mstx | input | ARADDR_WIDTH 2 | burst阅读事务第一个阅读传输地址,高2bit是为了片选axi slave | ||

| ARLEN_mstx | input | 8 | 该数值 1意味着这次读事务。RDATA个数 | ||

| ARSIZE_mstx | input | 3 | RDATA中有效byte大小 | ||

| ARBURST_mstx | input | 2 | burst传输类型 | ||

| ARVALID_mstx | input | 1 | AR所有所有控制信息都有效有效 | ||

| ARREADY_mstx | output | 1 | AR准备接收通道所有控制信息 | ||

| R | RID_mstx | output | RID_WIDTH | 读事务ID | |

| RDATA_mstx | output | RDATA_WIDTH | 读数据 | ||

| RRESP_mstx | output | 2 | 阅读反馈表示阅读传输的状态 | ||

| RLAST_mstx | output | 1 | 读取事务中最后一个读取数据 | ||

| RVALID_mstx | output | 1 | R通道所有数据信息有效 | ||

| RREADY_mstx | input | 1 | R准备接收通道所有数据信息 | ||

| B | BID_mstx | output | BID_WIDTH | 写事务ID | |

| BRESP_mstx | output | 2 | 写响应 | ||

| BVALID_mstx | output | 1 | B通道所有写反馈信息有效 | ||

| BREADY_mstx | input | 1 | B通道所有写反馈信息准备接收 |

| Group | Channel | Signal | Direction | Width(bits) | Description |

|---|---|---|---|---|---|

| ACLK | input | 1 | 时钟 | ||

| ARSTn | input | 1 | 复位,低有效 | ||

| SLV_IOx | AW | AWID_slvx | output | AWID_WIDTH+2 | AW通道ID宽度,高2bit用于标记Master |

| AWADDR_slvx | output | AWADDR_WIDTH | burst写事务第一个WDATA的地址 | ||

| AWLEN_slvx | output | 8 | 该数值+1就表示此次写事务的WDATA个数 | ||

| AWSIZE_slvx | output | 3 | WDATA中有效byte大小 | ||

| AWBURST_slvx | output | 2 | burst传输类型 | ||

| AWVALID_slvx | output | 1 | AW所有控制信息有效 | ||

| AWREADY_slvx | input | 1 | AW所有控制信息准备接收 | ||

| W | WDATA_slvx | output | WDATA_WIDTH | 写数据 | |

| WLAST_slvx | output | 1 | 写事务中的最后一个写数据 | ||

| WVALID_slvx | output | 1 | W通道所有数据信息有效 | ||

| WREADY_slvx | input | 1 | W通道所有数据信息准备接收 | ||

| AR | ARID_slvx | output | ARID_WIDTH+2 | 读事务ID,高2bit用于标记Master | |

| ARADDR_slvx | output | ARADDR_WIDTH | burst读事务第一个读传输地址 | ||

| ARLEN_slvx | output | 8 | 该数值+1就表示此次读事务的RDATA个数 | ||

| ARSIZE_slvx | output | 3 | RDATA中有效byte大小 | ||

| ARBURST_slvx | output | 2 | burst传输类型 | ||

| ARVALID_slvx | output | 1 | AR通道所有控制信息有效 | ||

| ARREADY_slvx | input | 1 | AR通道所有控制信息准备接收 | ||

| R | RID_slvx | input | RID_WIDTH+2 | 读事务ID,高2bit用于标记Master | |

| RDATA_slvx | input | RDATA_WIDTH | 读数据 | ||

| RRESP_slvx | input | 2 | 读反馈,表明读传输的状态 | ||

| RLAST_slvx | input | 1 | 读事务中的最后一个读数据 | ||

| RVALID_slvx | input | 1 | R通道所有数据信息有效 | ||

| RREADY_slvx | output | 1 | R通道所有数据信息准备接收 | ||

| B | BID_slvx | input | BID_WIDTH+2 | 写事务ID,高2bit用于标记Master | |

| BRESP_slvx | input | 2 | 写响应 | ||

| BVALID_slvx | input | 1 | B通道所有写反馈信息有效 | ||

| BREADY_slvx | output | 1 | B通道所有写反馈信息准备接收 |

| Parameter | Units | Description |

|---|---|---|

| AWID_WIDTH | bit | AW通道ID宽度 |

| AWADDR_WIDTH | bit | AW通道地址宽度 |

| WDATA_WIDTH | bit | W通道数据宽度 |

| ARID_WIDTH | bit | AR通道ID宽度 |

| ARADDR_WIDTH | bit | AR通道地址宽度 |

| RID_WIDTH | bit | R通道ID宽度 |

| RDATA_WIDTH | bit | R通道数据宽度 |

| BID_WIDTH | bit | B通道ID宽度 |

2.2. decoder

解码器的作用根据awaddr的高2bit或araddr的高2bit来片选访问的axi slave,那么如何表示片选到这个slave呢?

这里给出的思路是,AW、W和AR通道的控制信息实体或数据实体直接连接到每一个arbiter上,decoder只需通过valid信号表明片选。即

而R、B通道则需要片选结果将相应的控制信息、数据信息输入给AXI Master

| Channel | Signal | Direction | Width(bits) | Description |

|---|---|---|---|---|

| ACLK | input | 1 | 时钟 | |

| ARSTn | input | 1 | 复位,低有效 | |

| AW | AWSEL | input | 2 | 即AWADDR的高2bit,用于片选 axi slave |

| AWVALID | input | 1 | AW所有控制信息有效 | |

| AWREADY | output | 1 | AW所有控制信息准备接收 | |

| AWVALID_slv | output | 4 | 输出给axi slave的awvalid | |

| AWREADY_slv | input | 4 | 输出给axi slave的awready | |

| W | WVALID | input | 1 | W通道所有数据信息有效 |

| WREADY | output | 1 | W通道所有数据信息准备接收 | |

| WVALID_slv | input | 4 | 输入给axi slave的wvalid | |

| WREADY_slv | output | 4 | 输入给axi slave的wready | |

| AR | ARSEL | input | 2 | 为araddr的高2bit |

| ARVALID | input | 1 | AR通道所有控制信息有效 | |

| ARREADY | output | 1 | AR通道所有控制信息准备接收 | |

| ARVALID_slv | input | 4 | 输入给axi slave的arvalid | |

| ARREADY_slv | output | 4 | 输入给axi slave的arready | |

| R | RID | output | RID_WIDTH | axi slave发来的R通道ID |

| RDATA | output | RDATA_WIDTH | axi slave发来的R通道读数据 | |

| RRESP | output | 2 | axi slave发来的R通道反馈信息 | |

| RLAST | output | 1 | axi slave发来的R通道最后一个数据有效 | |

| RVALID | output | 1 | R通道所有数据信息有效 | |

| RREADY | input | 1 | R通道所有数据信息准备接收 | |

| RID_slv | input | RID_WIDTH×4 | axi slave发来的R通道ID | |

| RDATA_slv | input | RDATA_WIDTH×4 | axi slave发来的R通道读数据 | |

| RRESP_slv | input | 2×4 | axi slave发来的R通道反馈信息 | |

| RLAST_slv | input | 1×4 | axi slave发来的R通道最后一个数据有效 | |

| RVALID_slv | input | 4 | axi slave发来的R通道有效标志 | |

| RREADY_slv | output | 4 | 向axi slave输入的R通道准备标志 | |

| B | BID | output | BID_WIDTH | axi slave发来的B通道ID |

| BRESP | output | 2 | axi slave发来的B通道反馈信息 | |

| BVALID | output | 1 | B通道所有写反馈信息有效 | |

| BREADY | input | 1 | B通道所有写反馈信息准备接收 | |

| BID_slv | input | BID_WIDTH×4 | axi slave发来的B通道ID | |

| BRESP_slv | input | 2×4 | axi slave发来的B通道反馈信息 | |

| BVALID_slv | input | 4 | axi slave发来的B通道信息有效 | |

| BREADY_slv | output | 4 | 输入给axi slave的B通道准备 |

| Parameter | Units | Description |

|---|---|---|

| RID_WIDTH | bit | AXI R通道的ID位宽 |

| RDATA_WIDTH | bit | AXI R通道的读数据位宽 |

| BID_WIDTH | bit | AXI B通道的ID位宽 |

2.3. axi_round_robin_arbiter

此处的arbiter与decoder功能类似的,只不过arbiter的片选不是axi slave控制,而是根据轮询算法控制

对于B、R通道的控制信息和数据信息直接连接在每一个decoder上,arbiter只需控制valid和ready即可表示仲裁。

而AW、W和AR通道则需要根据仲裁结果片选相应的信号输出给AXI Slave

| Channel | Signal | Direction | Width(bits) | Description |

|---|---|---|---|---|

| ACLK | input | 1 | 时钟 | |

| ARSTn | input | 1×4 | 复位,低有效 | |

| AW | AWID_mst | input | (AWID_WIDTH+2)×4 | 写事务ID,高2bit用于标记Master |

| AWADDR_mst | input | AWADDR_WIDTH×4 | burst写事务第一个WDATA的地址 | |

| AWLEN_mst | input | 8×4 | 该数值+1就表示此次写事务的WDATA个数 | |

| AWSIZE_mst | input | 3×4 | WDATA中有效byte大小 | |

| AWBURST_mst | input | 2×4 | burst传输类型 | |

| AWVALID_mst | input | 1×4 | 各axi master输入的awvalid | |

| AWREADY_mst | output | 1×4 | 输出给各axi master的awready | |

| AWID | output | AWID_WIDTH | 写事务ID | |

| AWADDR | output | AWADDR_WIDTH | burst写事务第一个WDATA的地址 | |

| AWLEN | output | 8 | 该数值+1就表示此次写事务的WDATA个数 | |

| AWSIZE | output | 3 | WDATA中有效byte大小 | |

| AWBURST | output | 2 | burst传输类型 | |

| AWVALID | output | 1 | 输入给axi slave的awvalid | |

| AWREADY | input | 1 | 输入给axi slave的awready |

| Channel | Signal | Direction | Width(bits) | Description |

|---|---|---|---|---|

| W | WDATA_mst | input | WDATA_WIDTH×4 | 写数据 |

| WLAST_mst | input | 1×4 | 写事务中的最后一个写数据 | |

| WVALID_mst | input | 1×4 | 各axi master输入的wvalid | |

| WREADY_mst | output | 1×4 | 输入给各axi master的wready | |

| WDATA | output | WDATA_WIDTH | 写数据 | |

| WLAST | output | 1 | 写事务中的最后一个写数据 | |

| WVALID | output | 1 | W通道所有数据信息有效 | |

| WREADY | input | 1 | W通道所有数据信息准备接收 |

| Channel | Signal | Direction | Width(bits) | Description |

|---|---|---|---|---|

| AR | ARID_mst | input | (ARID_WIDTH+2)×4 | 读事务ID,高2bit用于标记Master |

| ARADDR_mst | input | ARADDR_WIDTH×4 | burst读事务第一个读传输地址 | |

| ARLEN_mst | input | 8×4 | 该数值+1就表示此次读事务的RDATA个数 | |

| ARSIZE_mst | input | 3×4 | RDATA中有效byte大小 | |

| ARBURST_mst | input | 2×4 | burst传输类型 | |

| ARVALID_mst | input | 1×4 | AR通道所有控制信息有效 | |

| ARREADY_mst | output | 1×4 | AR通道所有控制信息准备接收 | |

| ARADDR | output | ARADDR_WIDTH | burst读事务第一个读传输地址 | |

| ARLEN | output | 8 | 该数值+1就表示此次读事务的RDATA个数 | |

| ARSIZE | output | 3 | RDATA中有效byte大小 | |

| ARBURST | output | 2 | burst传输类型 | |

| ARVALID | output | 1 | 给axi slave输入的arvalid | |

| ARREADY | input | 1 | 输入给axi slave的arready |

| Channel | Signal | Direction | Width(bits) | Description |

|---|---|---|---|---|

| R | RSEL | input | 2 | RID的高2bit,用于片选axi master |

| RVALID | input | 1 | R通道所有数据信息有效 | |

| RREADY | output | 1 | R通道所有数据信息准备接收 | |

| RVALID_mst | output | 4 | 输入给各axi master发来的R通道有效标志 | |

| RREADY_mst | input | 4 | 各axi master输出的R通道准备标志 |

| Channel | Signal | Direction | Width(bits) | Description |

|---|---|---|---|---|

| B | BSEL | input | 2 | BID的高2bit,用于片选axi master |

| BVALID | input | 1 | B通道所有写反馈信息有效 | |

| BREADY | output | 1 | B通道所有写反馈信息准备接收 | |

| BVALID_mst | output | 4 | 输入给各axi master发来的B通道信息有效 | |

| BREADY_mst | input | 4 | 给axi master输出的B通道准备 |

| Parameter | Units | Description |

|---|---|---|

| AWID_WIDTH | bit | AXI AW通道的ID位宽 |

| AWADDR_WIDTH | bit | AXI AW通道的地址位宽 |

| WDATA_WIDTH | bit | AXI W通道的数据位宽 |

| ARID_WIDTH | bit | AXI AR通道的ID位宽 |

| ARADDR_WIDTH | bit | AXI AR通道的地址位宽 |

3. 逻辑设计

AXI_Bus_Matrix_4x4 设计 - 逻辑设计部分

4. 测试

由于decoder完成的就是片选功能,因此不作单独测试

4.1. axi_round_robin_arbiter

solo测试

主要用于AXI协议的solo测试,只有一个axi master和axi slave进行通信,先写再读

先上transcript,可见读写握手均成功

然后是各通道的波形,这里只展示master这一端

●

可见当握手成功后,优先级发生了改变

●

从grant FIFO中读出grant就开始握手,当握手完成后,就开始读新的grant。构成了AW CHANNEL和W CHANNEL的流水

●

注意此处bid_mst表示的是4个axi master 的输入bid拼接,即axi slave将bid和bresp直连到每一个axi master了

●

这个与AW通道逻辑类似

●

这个与B CHANNEL类似

3v1写测试

主要用于对多个AXI MASTER仲裁功能的测试,即令索引为0、2、3的AXI Master同时请求写时,仲裁调度功能能够如期实现。

先上transcript

与AXI Master 0握手成功: 与AXI Master 2握手成功: 与AXI Master 3握手成功:

然后是各通道的波形:

●

如下图所示, 初始时最高优先级是Master0,故先让它完成AW 通道握手。之后最高优先级为Master1,但是Master1的awvalid为0,所以grant赋予了Master2,等到AXI Slave的awready为高时就与AXI Master2握手。

最终与AXI Master3握手(图中未画出)完成测试

注意此处设定是AXI Slave完成AW通道握手之后awready拉低,等到B通道握手完成后awready拉高。实际应用中则不是这样,而是在AXI Slave中加入一个FIFO缓存AW通道控制信号,并且将FIFO的full取非后作为awready信号。

●

如图所示,从FIFO中读出grant为4’b0001之后,开始与AXI Master0握手,当wlast[0]为高时表示握手成功,继续读新的grant

●

这个就是纯粹的片选

3v1读测试

用于对多个AXI MASTER仲裁功能的测试,即令索引为0、1、3的AXI Master同时请求读时,仲裁调度功能能够如期实现。

此处略去波形图

4.2. axi_bus_matrix_4x4

4v1写测试

多个AXI MASTER仲裁功能的测试,即令索引为0、1、2、3的AXI Master同时请求写时,总线矩阵能否如期写入

设定的测试用例如下

AXI Master 0:

awid = 8'd0,

awaddr = 8'h00,

awlen = 8'd4,

awsize = 3'd2,

awburst = 2'd2,

wdata = 32'd0,32'd1,...,32'd3

AXI Master 1:

awid = 8'd10,

awaddr = 8'h10,

awlen = 8'd5,

awsize = 3'd2,

awburst = 2'd2,

wdata = 32'd4,32'd5,...,32'd8

AXI Master 2:

awid = 8'd20,

awaddr = 8'h20,

awlen = 8'd6,

awsize = 3'd2,

awburst = 2'd2,

wdata = 32'd9,32'd10,...,32'd14

AXI Master 3:

awid = 8'd30,

awaddr = 8'h30,

awlen = 8'd7,

awsize = 3'd2,

awburst = 2'd2,

wdata = 32'd15,32'd16,...,32'd21

测试transcript如下

从transcript中可以看到AXI Master0、1、2、3依次与Slave0完成AW握手,并且Slave0成功将W通道的数据计入FIFO,后根据awlen再从FIFO中读出并通过B通道与正确的AXI Master完成写反馈握手。

需要说明的是tb中slave的逻辑:这里的slave逻辑与axi_round_robin_arbiter_tb中的slave逻辑不同,此处的slave在AW通道和W通道分别设置AW_FIFO和W_FIFO(用mailbox实现)不断收集这两个通道的数据。如果能够读出AW_FIFO值的话,状态机启动,并根据awlen信号从W_FIFO读出数据,读出成功则通过B通道给一个反馈。

真正的Slave模块也可以这么设计

4v4写测试

未完待续