本文介绍了由它们组成的各种集成逻辑门和各种组合逻辑电路。这些电路的共同特点是,当前的输出完全取决于当前的输入,与过去的输入无关,它们没有记忆功能。在数字系统中,通常需要具有记忆功能和存储数字信息的逻辑部件。触发器是具有记忆功能和存储数字信息的基本逻辑电路。本章主要介绍了集成触发器的逻辑功能及其工作特性。

参考:总结电路时序波形绘制方法

- Visio

- Timegen

- WaveDrom 参考:好物分享:画时序图利器AndyTiming 参考:画出你最漂亮的数字时序图—WaveDrom

一、具体功能

参考:(备份)数字电路与数字电子技术(第2版) 岳怡

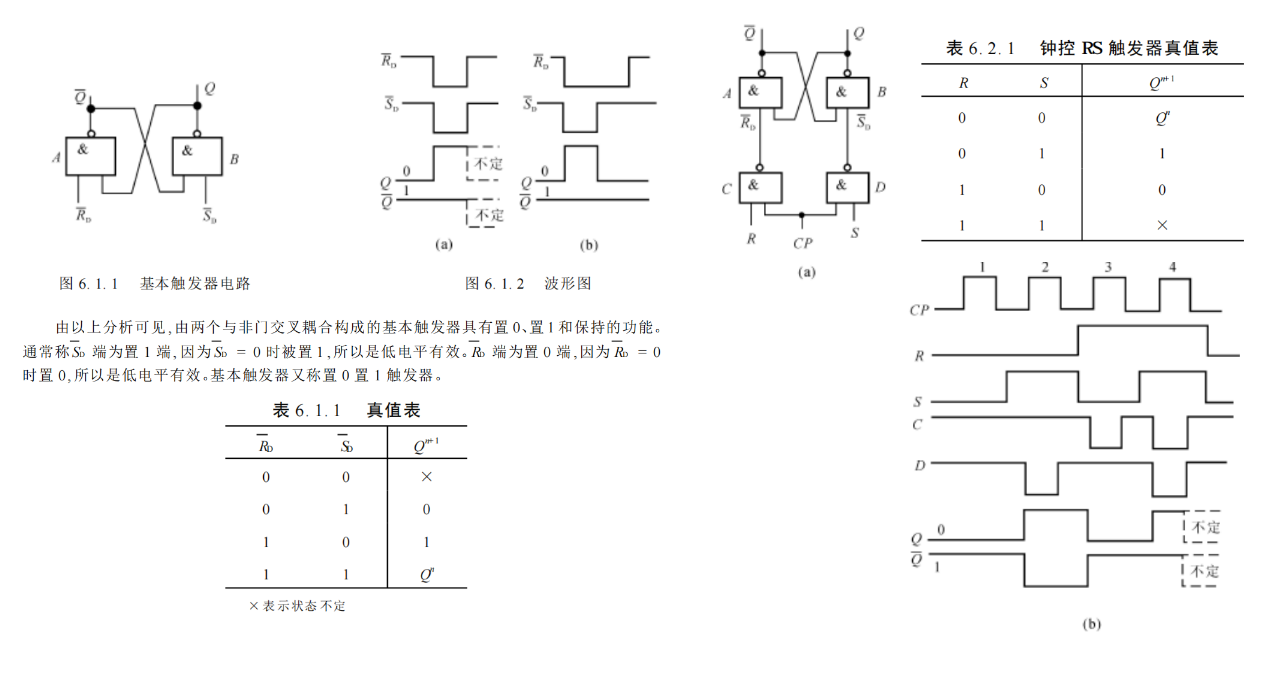

1.基本触发器

2.钟控触发器

上述基本R Sb只要输入信号发生变化,触发器状态就会根据其逻辑功能发生变化。在实际使用中,触发器通常需要在一定的时间节拍。这就要求触发器在翻转时刻受时钟脉冲(CP)各种钟控触发器由输入信号决定。按功能分钟控制RS触发器、D触发器、T触发器及JK触发器。

(1 钟控RS触发器

当时钟脉 CP = 0 时, C门和 D 门输出均为 1 ,不可能添加输入信号, 基本触 只有 CP = 1 时, 输入信号 R, S 通过引导门是可能的 C, D 加入基本触发器。

(2 钟控D触发器

钟脉冲触发器由四个和非门组成CP为低电平(CP = 0)触发器不接收输入信号,状态保持不变;当时钟脉冲CP为高电平(CP=1)触发器接收输入信号,状态转换。这种钟控方为电位触发。 因此,在CP= 1.触发器将连续翻转,即钟控触发器的空翻。如果要求在CP=当触发器只翻转一次时,时钟脉冲CP宽度要求极其苛刻。

(2 钟控T触发器

(2 钟控JK触发器

在钟控RS触发器中R=S=禁止1,因为它可能会使触发器的状态不确定。JK触发器是为了取消这一禁产生的。

三、主从触发器

为了解决钟控触发器的空翻问题,必须改进电路结构。目前常用的结构是主触发器。

4.边缘触发器

二、数字电路布局设计

参考:ch3-数字电路地图设计设计

1.从版图到原理图

请绘制与地图(如下图所示)对应的电路图(输入为A、B,输出为Y)

三、时序图

1、AndyTiming

这个工具是2004年的原因Andy Clark开发的初衷是帮助工程师快速方便地绘制时序图,它可以绘制波形图工具(AndyTiming) 绿色版本下载,绿色软件不需要安装,大小约400KB。下载后解压打开AndyTiming.exe,主界面非常简单。 参考:好物分享:画时序图利器AndyTiming 基本的使用方法很简单,AndyTiming用符号代码代表单位时间内的波形,