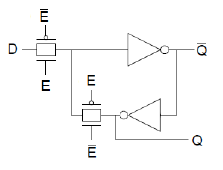

原创文章 latch(锁定器)电路图结构如下  当 E = 1 时,latch直传(transparent),D端信号的变化会在Q端立即反应; 当 E = 0 时,latch关断(closed),Q立即关闭D端的值。 设计中使用Latch优点是面积小,功耗低于寄存器,可以从后电路进行time borrowing,更容易满足setup time,然而坏处是STA分析不会那么直接。我们来看看介绍。Latch的Timing Path如何分析。

当 E = 1 时,latch直传(transparent),D端信号的变化会在Q端立即反应; 当 E = 0 时,latch关断(closed),Q立即关闭D端的值。 设计中使用Latch优点是面积小,功耗低于寄存器,可以从后电路进行time borrowing,更容易满足setup time,然而坏处是STA分析不会那么直接。我们来看看介绍。Latch的Timing Path如何分析。

Timing borrowing 由于锁定器在半个始终周期内直接连接,数据到达的时间限制更宽,但当锁定器数据传输到触发器时,数据保持稳定的时间会减少,因此后续的逻辑延迟会减少。timing borrowing.(这是小白初学者自己的理解,如果有错误,希望大家能指正)。

Look up latch 为了完成DFT工作时,需要将扫描链插入芯片内部,将不同时钟域的寄存器串联起来。 未加入Look up latch电路图和时序图 因为时钟不同,所以CLK1与CLK2之间存在skew,可大可小,所以FF1.CLK1—FF1.Q—FF2.SI这段延时比skew小,造成hold timing违例。

加入Look up latch后电路图和时序图

latch后面的寄存器可以修理hold原因是,修理hold可以增加数据路径上的延迟,因此当插入可以增加部分延迟并插入时latch后,由于timingborrow,后寄存器capture提前了半个周期也有利于hold修复。