摘要

不同的电流镜拓扑通过模拟分析和现代地图设计方法的利用进行了优化。 低压、短通道电路的研究 1.5 V 在电源电压下工作。电流镜在 Virtuoso Cadence CAD 工具中使用 0.11 μm 仿真设计技术。 这项调查表明,可以通过使用级联技术和其他设计解决方案来获得高性能电路,这些解决方案可以减少由于非理想效应引起的比率误差。

背景

在过去的几十年里,微电子已经成为许多领域进步的动力,如信息技术、工业电子、医疗电子和汽车工业。 这些成就在微电子技术的发展和集成电路设计中使用的新设计电路解决方案中发挥了重要作用。

电流镜 (CM) 是集成电路 (IC) 设计中的基本构造块。 它们用作电流源或有源放大器负载 (Shtereva K., 2016, Kaur, J., 2017)。 电流镜偏置是模拟和数字电路设计中使用的一项重要技术。

目前,研究工作主要集中在标准上CMOS开发低压集成电路设计技术。 在 (Rakus, M., 2018) 中国研究了涉及驱动 (BD) MOS 晶体管和动态阈值 (DT) MOS 晶体管的设计方法。 三种不同的分析 CM 拓扑。 作者发现,与传统的栅极驱动拓扑相比,这两种技术都可以改进 Wilson 和级联 CM 降低最小输出电压 30%。 另一个小组 (Zohoori, S., 2018) 基于电流镜提出了一种 90 nm CMOS 中的低电压 (1 V)、低功率 (1.4 mW) 用于跨阻放大器 10 GBps 光通信。

本文介绍了,采用 0.11 μm CMOS 技术,使用 Virtuoso Cadence 计算机附加设计 (CAD) 工具。 比较了负载电流对电源电压依赖的模拟结果。

结论

基础电流镜

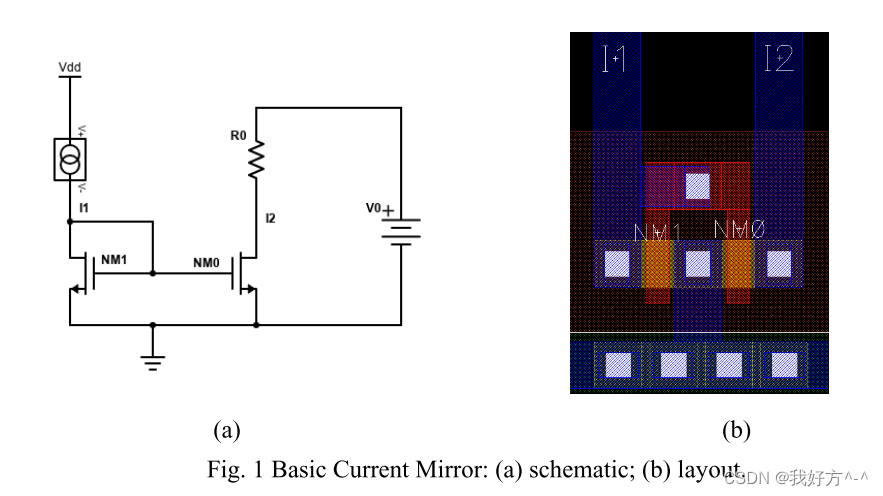

最简单的电流镜类型由两种匹配 n 沟道 MOS 晶体管组成。 图 1(a) 示意图显示,图 1(b) 显示基本电流镜的布局。

输入电流 I1 定义电流源。 输出电流 I二、复制或镜像I1。 NM1 二极管连接 MOS 因为晶体管 VDS1 = VGS因此,工作处于饱和状态。 一般而言,I2/I1 以下等式给出的比率(Allen, Ph. E., & Holberg, D. R., 2002): L1, L2 – NM1 和 NM0 通道长度, W1, W2 – NM1 和 NM0 通道宽度, VT1, VT2 z NM1 和 NM0 阈值电压, k1, k2 – NM1 和 NM0 跨导参数, λ – 调制通道长度。 因此,两个MOS晶体管是相同的集成电路VT1=VT2,k1=k二、处理。 如果 VDS1 = VDS2,则等式 (1) 可改写为:

输入电流 I1 定义电流源。 输出电流 I二、复制或镜像I1。 NM1 二极管连接 MOS 因为晶体管 VDS1 = VGS因此,工作处于饱和状态。 一般而言,I2/I1 以下等式给出的比率(Allen, Ph. E., & Holberg, D. R., 2002): L1, L2 – NM1 和 NM0 通道长度, W1, W2 – NM1 和 NM0 通道宽度, VT1, VT2 z NM1 和 NM0 阈值电压, k1, k2 – NM1 和 NM0 跨导参数, λ – 调制通道长度。 因此,两个MOS晶体管是相同的集成电路VT1=VT2,k1=k二、处理。 如果 VDS1 = VDS2,则等式 (1) 可改写为:

等式 (2) 负载与参考电流之间的理想比率 I2/I1。 比例与宽长比或纵横比成比例作为设计参数。 两个晶体管必须相同 1:1 的电流比。 基本电流镜中电流的不准确复制是由于通道长度调制等非理想效果造成的; 阈值电压偏移,两个晶体管不完美匹配。 基本电流镜的输出电阻如下: 输出电阻是衡量电路完善程度的重要指标。 基础的CM相对较低。 这种电流镜的主要优点是简单和小芯片面积。 推荐布局(图1(b))设计是为了最小化面积。

共源共栅电流镜 Cascode CM

由于以下原因,级联技术的使用减少了比例误差: (i) 输入输出电压的差异; (ii) 忽略通道长度调制; (iii) 并增加输出电阻。 然后,复制电流中的错误减少了。 2 中显示了:(a) 示意图,和 (b) 级联电流镜的布局。

级联可以由 3、4、5 或 6 晶体管的组成取决于当前复制所需的精度。 晶体管连接的许多问题是电源电压水平的提高,这与当前需要降低电源电压和芯片尺寸的微电子趋势相矛盾。 级联电流镜的输出电阻为 (Razavi, B. (2001): 级联电流镜的输出电阻远高于基本电流镜,因此负载电流对输出电压的变化非常稳定(Reshma,P.G.,2017)。 布局设计(图 2(b))确保降低寄生元件和镜子比率的失配。 四个晶体管必须饱和,以减少复制电流的误差。 二极管连接 NM1 和 NM3 饱和。 如果 NM2 泄漏极的输出电压至少为 Vdsat 的两倍(Vdsat0 和 Vdsat二、晶体管 NM0 和 NM2 饱和。 因此,所需的最低电源电压约为 1 V。

修改威尔逊共源共栅电流镜

修改威尔逊共源共栅电流镜的示意图(图3(一)是改进版的基本威尔逊电流镜。(斯宾塞,r . 2001)。由于插入的NM3晶体管,NM1 gate-source电压和NM0是相等的。负反馈的使用增加了输出电阻,这意味着目前的复制赌博。可以忽略电路的系统误差。图3所示的物理设计(b)。相似的标准共源共栅厘米。唯一的区别是,NM1和NM0晶体管连接不同,因此二极管连接NM右分支0晶体管。 获得的电流特性(图 6)表明,如果所有四个晶体管都处于饱和状态,则可以降低比率误差。 在这种情况下,电流复制和标准级联电路一样好。 正因为如此,这种结构在今天很少使用 CMOS 技术。

宽摆幅级联电流镜

(图 4 (a))宽摆幅级联电流镜是各种标准级联电流镜,用于低偏置电压 (Arif, M., 2012)。 这种宽摆幅级联共源共栅架构需要额外的电流镜支路来维护 NM2 处于饱和状态,使其饱和 Vdsat2 远低于普通级联电流镜。 输出电压摆幅高于通常的级联电流镜。 当然,该方案改善了输出摆幅,但也带来了与消耗相关的缺点,需要第二个稳定电流。 电路的基本功能如下,除外NM3外的晶体管均相同。 与另一个晶体管相比,这个单晶体管的沟渠 L 大约大 4 倍,以增加 NM2 饱和所需的压降。 另一种选择是分支1的电流大4倍,不利于电流镜的消耗。 由于级联从另一个参考电流偏置,选择级联的工作点 Vdsat 最小值允许更高的输出摆幅和更低的电源。

布局(图 4(b))由于晶体管占用了更多的空间,晶体管指的匹配不是很好 NM3。 这些调整可以通过应用来改善单个晶体管不匹配的虚拟或备用晶体管来改进。

自偏置级联电流镜

这种架构的优点(图 5 (a))它不需要像其他架构那样参考输入电流(Guha, K., 2017)。 电阻器采用参考电流 R1 产生。 正确的 VGS1 需要电阻器才能使所有四个晶体管饱和。 选择电阻器的值是提供驱动电流镜饱和的压降。 电阻值约为50 kΩ,芯片面积大。 另一个问题是实现低容差的高电阻电阻。 电阻器的尺寸可能比电流镜大 10 倍以上。 当然,在大规模方案中,这些电阻器可以布置成尽可能紧凑的块,但这并不排除可用的大空间。 图 5(b)显示了自偏置级联电流镜的布局。 图 6 显示电流镜不同拓扑结构的对比图。 红色是恒流 I1 = 10μA。 模拟结果(图6)显示,自偏共源共栅电流镜的电流复制是最好的,不需要参考电流。 当然,与温度相关的高容差电阻会稍微降低电流。 该方案是工业上最常用的方案之一,在许多复杂的设计中发挥着重要作用。 电流镜的其他重要参数,如电压摆幅、功耗、电源电压和布局尺寸,也取决于电流镜的拓扑。 级联晶体管数量的增加增加了电源,降低了电压摆幅,增加了芯片面积。 基本电流镜或宽摆幅电流镜应用于高压摆幅。 因此,拓扑的选择取决于系统或产品的要求,以平衡参数和芯片面积。

结论

本文比较了五种电流镜架构。 使用 Virtuoso Cadence 以 0.11 μm CMOS 模拟和布局设计技术。 模拟结果表明,输出电阻的增加导致电流复制的改善,并在各种变化下变得更加稳定。 输出电压摆幅是电流镜的另一个重要参数。 在选择最佳拓扑时,应该是权衡两者。