参考链接: 天天在用的ADC,你知道内部原理吗?

接近寄存器型ADC简称SAR ADC(SAR,Successive Approximation Register),它占据了大部分中等至高分辨率ADC市场。SAR ADC最高采样率可达5Msps,8-18分辨率。SAR架构允许高性能、低功耗ADC小尺寸包装适用于尺寸要求严格的系统。

1.SAR架构

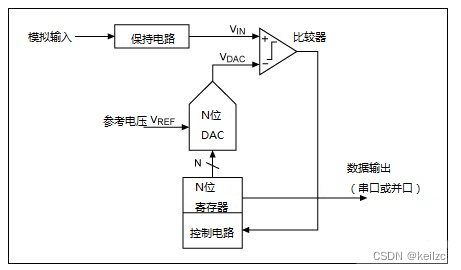

逐次逼近型ADC多步执行转换,转换步数等于ADC转换器中的位数。每一步都由ADC时钟驱动。每一个ADC时钟从结果到输出 位。ADC基于切换电容技术的内部设计。  尽管实现SAR ADC但其基本结构非常简单。如图所示,主要包括以下四个部分:采样保持电路(Sample and Hold)、比较器(Comp)、接近寄存器和控制电路(SARLOGIC)、D/A转换电路(DAC)。 输入电压Vin采样电压通过采样保持电路获得Vin,Vin与DAC的输出Vdac比较结果通过比较器传递给寄存器,一方面输出比较结果,另一方面控制DAC为了进行下一个转换,转换开关。

尽管实现SAR ADC但其基本结构非常简单。如图所示,主要包括以下四个部分:采样保持电路(Sample and Hold)、比较器(Comp)、接近寄存器和控制电路(SARLOGIC)、D/A转换电路(DAC)。 输入电压Vin采样电压通过采样保持电路获得Vin,Vin与DAC的输出Vdac比较结果通过比较器传递给寄存器,一方面输出比较结果,另一方面控制DAC为了进行下一个转换,转换开关。

2.逐次转换的过程

许多SAR ADC具有固有采样/保持功能的电容式DAC。电容式DAC模拟输出电压是根据电荷再分配的原理产生的。DAC在SAR ADC很常用。电容式DAC包括由N个按二进制加权排列的电容组成的阵列,如下图所示: 采样状态:Sa切换至VIN,采样期间Sb开关关闭合,电容充电至电压VIN。 保持状态:输入VIN断开,Sb断开开关,然后S1-S11切换到接地,Sa切换至VREF。 逐次逼近: 第一步是接近步骤。S1切换至VREF。VIN与VREF/2比较 2、如果MSB = 0,则与?VREF进行比较,S切换回接地。S2切换至VREF。 3、如果MSB = 1,则与?VREF进行比较,S1保持接地。S2切换至VREF。

重复以上步骤,直到LSB为止。输入电压与参考电压的比较可以简单地理解为二分法。首次与VREF如果/2比较,下次比较将根据上次比较结果确定MSB=1则与?VREF比较。如果MSB=0则与?VREF比较。以后决定和1/8VREF、 3/8VREF、 5/8VREF、 7/8VREF比较一下。循环直到输出LSB为止。

3.SAR ADC与其它ADC结构的比较

3.1与流水线ADC相比

流水线ADC采用并行结构,并行结构中的每个级别同时采样一个或多个层次。这种固有的并行结构提高了数据的吞吐率,但以功耗和延迟为代价。在这种情况下,所谓的延迟被定义为ADC采样到模拟输入和输出端获取量化数据的时差。例如,一条5级流水线ADC至少有5个时钟周期的延迟,SAR延迟只有一个时钟周期。需要注意的是,延迟的定义只是相对于ADC就吞吐率而言,并不意味着SAR内部时钟是吞吐率的多倍。流水线ADC为了降低对流水线上每一级的闪速,需要频繁校准数字误差ADC (即比较器)精度要求。而SAR ADC比较器的精度只需要等同于整个系统的精度。流水线ADC一般比同级别的好SAR需要更多的硅片面积。与SAR同样,精度高于12位的流水线ADC通常需要某种形式的微调或校准。

3.2与闪速ADC相比

闪速ADC每个比较器由大量的比较器组成,包括宽带、低增益预放器和锁定器。预放器必须仅用于提供增益,不需要高线性和高精度,这意味着只有比较器的门限值才需要更高的精度。因此,闪速ADC是目前转换速度最快的架构。

通常需要考虑闪速ADC的速度以及SAR DAC低功耗和小尺寸特性。尽管高速8位闪速ADC (及其折叠/内插变种)高达1.5Gsps采样速率(例如 MAX104 、 MAX106 和 MAX108 ),但是很难找到10位的闪速ADC,12位闪速(和更高位)ADC还没有商用产品。这是因为分辨率每提高一位,闪速ADC中比较器的个数将成倍增长,同时还要保证比较器的精度是系统精度的两倍。而在SAR ADC提高分辨率需要更准确的元素,但复杂性不会按指数率增加。当然,SAR ADC速度不能与闪速相匹配ADC相比较的。

3.3与Σ-Δ转换器相比

传统的过采样/Σ-Δ转换器一般用于带宽限制约22kHz数字音频应用。近来,一些宽带Σ-Δ转换器可达1MHz至2MHz分辨率为12-16的带宽。通常由高阶组成Σ-Δ调制器(如4级或更高)配合一个多位ADC和多位反馈DAC构成。Σ-Δ转换器有一个优点SAR ADC即使分辨率达到16-18位,也不需要特殊的微调或校准。由于该类型ADC采样速率远高于有效带宽,因此无需在模拟输入端增加快速滚降的抗混叠滤波器。后端数字滤波器处理。Σ-Δ转换器的过采样特性也可用于模拟输入中的任何系统噪声。

Σ-Δ转换器应以速率换取分辨率。因为最终采样需要多次采样(至少16倍,一般更多),这就需要Σ-Δ调制器内部模拟电路的工作速率远快于最终数据。数字抽取滤波器的设计也是一个挑战,并要消耗相当大的硅片面积。在不久的将来,最快的高分辨率Σ-Δ转换器的带宽不太可能比几兆赫兹高很多。

4.总结

综上所述,SAR ADC其主要优点是功耗低、功耗高 由于这些优点,分辨率高,精度高,尺寸小。SAR ADC通常与其它更大的功能集成。SAR结构的主要局限性是采样速率低,每个单元(如DAC和比较器),需要达到与整个系统相当的精度。

逐次逼近型ADC(SAR)的工作原理