DDR4 SDRAM结构和寻址

- DDR4 SDRAM封装及寻址

-

- DDR4 SDRAM引脚说明

- DDR4 SDRAM寻址及容量计算

- DDR4 SDRAM包装及电气特性

DDR4 SDRAM封装及寻址

本节先介绍DDR4 SDRAM输出输出引脚,然后根据输入输出引脚的定义DDR4 SDRAM阐述了寻址方法,最后简要介绍了设备封装。

DDR4 SDRAM引脚说明

将基于本节DDR4 SDRAM描述所有信号的功能。逻辑上,DDR4 SDRAM中数据通道和数据通道的边带信号采用三态输入输出,对应关键路径上的时钟、数据选通信号做了差分传输处理。就电气连接特性而言,只有部分电源和参考电压采用端接处理,而其他路径采用差分、三态和复用设计。 由于SDRAM核心密度越来越大,SDRAM上述总线的再利用变得更加重要。在功能方面,SDRAM总线由命令总线、地址总线和数据总线组成。因此,地址信息可以看作是命令信息的一部分SDRAM搜址需要与命令相结合。在DDR4 SDRAM命令或寻址分为两部分,激活命令(行寻址),读写命令(列寻址)。在行列地址搜索过程中,也有行列地址的情况,所以DDR4的操作变得更加复杂。DDR4的操作流程请参考相应的章节,本节对应I/O具体阐述信号,理解DDR4的I/O在操作过程中,对总线重用的理解将极大地有利于理解本章。

| 信号 | 类型 | 功能 |

|---|---|---|

| CK_t, CK_c | Input | 时钟:DDR四差分时钟工作,CK_t和CK_c是差分钟输入,设备在CK_t的上升沿和CK_c所有地址和样,输入信号控制在下降边的交点处。 |

| CKE, (CKE1) | Input | 时钟使能:CKE激活内部时钟信号和设备输入缓冲器和输出驱动器CKE上述时钟被禁止拉下。将CKE低电平提供预充电断电(Precharge PowerDown)和自刷新(Self-Refresh)操作(当所有BANK在空闲状态下触发)或提供激活电源(Power-Down)模式(当任何存储器中的行有效时触发)。CKE在自刷新模式下同步退出。当VREFCA和内部DQ Vref变得稳定后,必须在所有操作中保持(包括自刷新)CKE为高电平。除掉电模式期间CK_t,CK_c,ODT和CKE禁用外部输入缓冲器。新自刷期间禁用除CKE所有输入缓冲区。 |

| CS_n, (CS1_n) | Input | 片选信号:CS_n一般情况下,所有的命令都会被屏蔽。CS_n有多个信号RANK系统提供外部RANK片选。CS_n信号被视为DDR部分命令代码(参考命令真值表)。 |

| C0,C1,C2 | Input | 芯片ID:芯片ID仅用于通过TSV2、4、8高堆栈3DS选择堆栈组件的每个切片。ID被视为命令代码的一部分。(针对3DS堆叠芯片) |

| ODT, (ODT1) | Input | 芯片终端:ODT为高时使能DDR4 SDRAM内部的RTT_NOM终端电阻。ODT该技术是片上终结电阻,用于消除片上终端信号反射余波。启用后,对应X8配置 SDRAM颗粒,ODT仅适用每路DQ,DQS_t,DQS_c和DM_n / DBI_n / TDQS_t,NU / TDQS_c信号通路。对于x16配置,ODT应用于每个DQ,DQSU_t,DQSU_c,DQSL_t,DQSL_c,DMU_n和DML_n信号。模式寄存器是正确的OTD配置电阻,当MR模式寄存器1A11 = 1时(启用TDQS)启用OTD电阻。如果MR禁止编程RTT_NOM,则ODT引脚会被忽略。 |

| ACT_n | Input | 激活输入命令:ACT_n定义为与CS_n一起输入激活命令。DDR4 SDRAM使用ACT_n、CS_n、RAS_n / A16、CAS_n / A15和WE_n / A14具体组合表示操作命令,请参考DDR4命令真值表。RAS_n、CAS_n、和WE_n分别在A16,A15,A14.上传输,即部分地址和命令重用总线。ACT_n有效时RAS_n / A16,CAS_n / A15和WE_n / A14的输入将被视为行地址A16,A15和A14。 |

| RAS_n/A16. CAS_n/A15. WE_n /A14 | Input | 命令输入:RAS_n / A16,CAS_n / A15和WE_n / A14(以及CS_n)定义要输入的命令。注意,这些引脚具有复用功能。当ACT_n激活命令(参考真值表)用作低有效时的搜索地址A16,A15和A14,而当以ACT_n当它们是高度非激活的命令时,它们是用中定义的命令的引脚。 |

| DM_n/DBI_n/TDQS_t, (DMU_n/DBIU_n), (DML_n/DBIL_n) | Input output | 与数据总线相反,输入数据掩码:DM_n用于编写数据的输入掩码信号。 由于DDR4采用突发传输技术,对于非连续访问,在写访问期间,DM_n当信号对应的输入数据同时采样时,DM_n为LOW时,SDRAM屏蔽输入数据。DM_n信号在DQS上下沿采样。DM通过MR模式寄存器5中A10,A11,A12设置与DBI功能复用。对于x8设备,通过MR模式寄存器1A11设置启用DM或TDQS功能。 DBI_n是用于存储或写入识别数据的反相识别信号SDRAM数据是否反相处理。如果DBI_n如果是低电平,数据将在DDR4 SDRAM内部反转后存储/输出DBI_n正常输出为高电平。TDQS仅在X8中受支持 |

| BG0 - BG1 | Input | 存储体组(BANK Group)输入:BG0-BG将激活、读取、写入或预充电命令应用于哪个存储组定义。BG0还确定在MRS在周期内访问哪种模式的寄存器。X4 / 8具有BG0和BG1,但X16仅具有BG0 |

| BA0 - BA1 | Input | BANK地址输入:BA0-BA激活、读取、写入或预充电命令应用定义BANK。 还确定了存储体地址MRS在周期内访问哪种模式的寄存器。 |

| A0 - A17 | Input | 地址输入:为ACTIVATE命令提供行地址,为Read / Write命令提供列地址,以从相应存储体的存储器阵列中选择一个位置。注意在DDR4中行列地址是复用的,而地址的高位又与命令复用。其中(A10 / AP,A12 / BC_n,RAS_n / A16,CAS_n / A15和WE_n / A14具有其他功能,请参见信号定义。地址输入还在模式寄存器设置命令期间提供操作码.A17仅针对x4组态。 |

| A10 / AP | Input | 自动预充电:在读/写命令期间对A10进行采样,以确定是否应在读/写操作后对所访问的存储体执行自动预充电。(高:自动预充电;低:无自动预充电)。在预充电命令期间对A10进行采样,以确定预充电是适用于一个存储库(A10低电平)还是适用于所有存储库(A10高电平)。如果只预充一个Bank,则按Bank地址选择该Bank。在ACT_n有效,即发送激活命令时传输行地址。 |

| A12 / BC_n | Input | 突发斩波:在读取和写入命令期间对A12 / BC_n进行采样,以确定是否将执行突发斩波。(高,无突发斩波;低:突发斩波)。 有关详细信息,请参见命令真值表。 |

| RESET_n | Input | 异步复位:RESET_n为低电平时复位有效,而RESET_n为高电平时无效。 在正常操作期间,RESET_n必须为高电平。RESET_n是CMOS轨到轨信号,直流高电平和低电平分别为VDD的80%和20%。 |

| DQ | Input output | 数据输入/输出:双向数据总线。如果通过模式寄存器启用了CRC,则在数据突发末尾添加CRC。 |

| DQS_t, DQS_c,DQSU_t, DQSU_c,DQSL_t, DQSL_c | Input output | 数据选通:和读数据一起输出,和写数据一起输入,并与读取数据边缘对齐,以写入数据为中心。对于x16,DQSL对应于DQL0-DQL7上的数据。DQSU对应于DQU0-DQU7上的数据。 数据选通脉冲DQS_t,DQSL_t和DQSU_t分别与差分信号DQS_c,DQSL_c和DQSU_c配对,以在读写期间向系统提供差分对信号。 DDR4 SDRAM仅支持差分数据选通,不支持单端。 |

| TDQS_t, TDQS_c | output | 终端数据选通:TDQS_t / TDQS_c仅适用于x8 DRAM。通过MR1中的模式寄存器A11 = 1启用,DRAM将在TDQS_t / TDQS_c上启用与DQS_t / DQS_c相同的终端电阻功能。 当通过MR1中的模式寄存器A11 = 0禁用时,DM / DBI / TDQS将提供数据屏蔽功能或取决于MR5的数据总线反转。未使用A11、12、10和TDQS_c, x4 / x16 DRAM必须通过MR1中的模式寄存器A11 = 0禁用TDQS功能。 |

| PAR | Input | 命令和地址奇偶校验输入:DDR4在具有MR设置的DRAM中支持偶校验。通过MR5中的寄存器启用后,DRAM会使用ACT_n,RAS_n / A16,CAS_n / A15,WE_n / A14,BG0-BG1,BA0-BA1,A17-A0计算奇偶校验。输入奇偶校验应保持在时钟的上升沿,并同时与CS_n LOW的命令和地址保持一致 |

| ALERT_n | Input output | 警告:它具有多种功能,例如CRC错误标志,命令和地址奇偶校验错误标志,作为输出信号指示错误。如果CRC中有错误,则Alert_n在一段时间间隔内变为LOW,然后返回HIGH。如果命令地址奇偶校验中存在错误,则Alert_n会在相当长的一段时间内变为低电平,直到继续进行DRAM内部恢复事务为止。 在连通性测试模式下,此引脚用作输入。 是否使用此信号取决于系统。 如果未作为信号连接,则必须将ALERT_n引脚绑定到板上的VDD |

| TEN | Input | 连通性测试模式启用:X16器件上必选,并且密度等于或大于8Gb的x4 / x8上为可选输入。此引脚中的高电平将使连通性测试模式与其他引脚一起运行。 它是CMOS轨到轨信号,AC高低分别为VDD的80%和20%。 是否使用此信号取决于系统。可以通过一个弱下拉电阻将DRAM内部将此引脚拉低至VSS。 |

| NC | 无连接 | 不存在内部电气连接 |

| VDDQ | 供应 | DQ电源:1.2 V +/- 0.06 V |

| VSSQ | 供应 | DQ地 |

| VDD | 供应 | 电源:1.2 V +/- 0.06 V |

| VSS | 供应 | 地 |

| VPP | 供应 | DRAM激活电源:2.5V(最低2.375V,最高2.75V) |

| VREFCA | 供应 | CA参考电压 |

| ZQ | 供应 | ZQ校准参考引脚 |

注意 仅输入引脚(BG0-BG1,BA0-BA1,A0-A17,ACT_n,RAS_n / A16,CAS_n / A15,WE_n / A14,CS_n,CKE,ODT和RESET_n)不提供端接。

DDR4 SDRAM寻址和容量计算

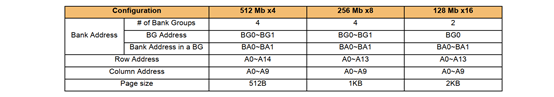

本节以DDR4 8Gb芯片为例对DDR4的容量和寻址进行阐述。 对应SDRAM器件而言,常见的单Die数据位宽为4Bit(x4),8Bit(x8)和16Bit(x16)配置。对于现代的64Bit计算机而言,需要多个SDRAM拼接才可以完成所需的数据位宽。以常见的x8配置的SDRAM颗粒而言,需要8颗芯片拼接完成64Bit的数据位宽,这样,在Memory controller寻址一个数据单元时,8组芯片都会被选中,因此这8组芯片公用一个Cs_n信号,我们称之为1个RANK。 综上,SDRAM的容量由两个重要参数,RANK的数据位宽和寻址深度。当使用多个芯片组成RANK时,RANK的数据位宽会增大,但是一般而言,不会改变寻址深度(如果这样需要使用高位地址做译码,在高速电路中不建议这么做)。SDRAM容量=单科芯片数据位宽 * RANK中芯片数 * 芯片寻址深度。 以64-Bit的8GB系统而言,我们选用x8配置芯片,那么一个RANK中需要8颗这种芯片,则寻址深度=(8192Gb * 8Bit)/ (8 Bit * 8) = 1024Mb。而单颗芯片容量为1024Mb * 8Bit = 8Gb = 1GB。 在SDRAM内部,存储单元被划分成行和列,一片区域的由行和列组成的区域我们成为BNAK(存储体),一个BNAK共用一个敏感信号放大器和寻址单元。这和SDRAM的原理和架构有关,不是本章重点,请参考SDRAM的晶体管原理,本章中会把存储信息的晶体管和电容抽象为存储单元,从而对SDRAM的寻址和组织形式进行介绍。在DDR4中,新增了BANK GROUP的概念,一颗存储芯片中会有4个或者8个Bank Group,使用BG[1:0]或BG[2:0]进行寻址;而每个BG组中有4个BANK存储体,使用BA[1:0]寻址;每个BANK中可以存在多个行,A0-A17用来寻址行,(只有16Gb容量DDR4存在A17),行地址从A14到A17不等,由容量和位宽决定;在每一行中,又存在多个列,DDR4协议规定每行为1024列,即页大小为1024,使用A0-A9进行寻址。

2 Gb寻址表

4 Gb寻址表 8 Gb寻址表 16Gb寻址表

4 Gb寻址表 8 Gb寻址表 16Gb寻址表

DDR4 SDRAM封装和电气特性

DDR4协议规定了两种封装形式,分别对应于X4/X8配置和X16配置。 DDR4 SDRAM x4 / x8和x16组件有2组3列共6列电气焊球。可能还有其他非活动的焊球列用于机械支撑。 DDR4 SDRAM的封装图如下:

X4/X8 DDR4 封装 X16 DDR4 封装